Аналогово-цифровой преобразователь (АЦП)

Введение.

Аналого–цифровой преобразователь (АЦП) предназначен для формирования 12-битного цифрового кода, пропорционального аналоговому входному напряжению.

Состав и принцип работы

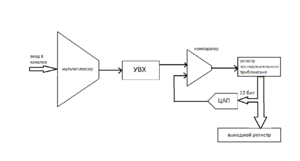

Модуль представляет собой АЦП последовательного приближения и входного мультиплексора 8 в 1 с дешифратором 3 в 8. Структурная схема представлена на рисунке

АЦП последовательного приближения состоит из резистивного ЦАП, модуля SAR14, SAH (УВХ), компаратора, модуля тестирования выхода ЦАП, а также модулей дерева clock и цифровой управляющей логики.

Аналоговое входное напряжение хранится в блоке УВХ (SAH). Исполнение алгоритма последовательного приближения обеспечивает блок SAR. Выходы ЦАП выставляются согласно значению из регистра SAR. Компаратор выполняет сравнение значений напряжений из УВХ и ЦАП и результат сравнения подается на вход SAR.

Резистивный ЦАП состоит из двух каскадов, каждый из которых обеспечивает разрешение 6 бит. Каждый единичный элемент каскада состоит из одного резистора. Топологически эти элементы расположены симметрично относительно центра (common centroid) для уменьшения разброса параметров. Выходы первого каскада не буферизируются, поэтому для уменьшения систематической ошибки единичные элементы второго каскада имеют большее сопротивление (300 Ом по сравнению с 75 Ом).

Выходной буфер представляет собой неинвертирущий ОУ с коэффициентом усиления один. Формирователь внутреннего опорного напряжения от источника аналогового напряжения 1,8 В обеспечивает напряжение 1,2 В при Uист = 1,8 В.Типичный ток потребления ОУ составляет 250 мкА (не учитывая выходной ток). В выключенном состоянии типичный ток потребления ОУ составляет 30 нА.

Аналоговое входное напряжение, Vin, хранится в устройстве выборки/хранения SAH/УВХ. Данные записываются по сигналу Start передним фронтом clock половинной частоты и хранятся с течение цикла преобразования на конденсаторе.

Входная частота делится на 28 и на 2, с формированием дополнительного синхросигнала с фазой, сдвинутой на 90 градусов (блок CLK_div). По сигналу Start в соответствии с прямым и смещенным синхросигналами формируются сигналы сброса установки SAR.

Входной мультиплексор данных включает в себя регистр выбора адреса входных данных, дешифратор 3 в 8 и проходные ключи. Адрес записывается в регистр по сигналу CK, формируемому в блоке SAR и сохраняется до следующего CK, что позволяет закончить цикл преобразования данных с текущего входа, даже если адрес сменился. До появления первого сигнала CK по сигналу сброса по умолчанию устанавливается вход данных DIN<0>.

Управление АЦП

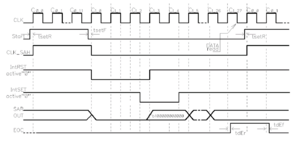

В начале каждого цикла преобразования SAR по сигналу Start и переднему фронту сигнала CLK N-разрядный регистр в составе SAR сначала сбрасывается в 0, а затем устанавливается в значение, равное половине шкалы преобразования, N’b100…00, где MSB - лог. «1». При этом выход ЦАП устанавливается в ½ опорного напряжения (VRF). После этого компаратор сравнивает Vin(выход УВХ) и VDAC . Если Vin больше, чем VDAC , выход компаратора устанавливается в лог. «1», при этом MSB N-разрядного регистра остается в «1»; Если Vin меньше, чем VDAC , выход компаратора устанавливается в лог. «0», при этом MSB сбрасывается в «0». Следующий по старшинству разряд устанавливается в «1» и процесс сравнения повторяется. Последовательность повторяется для всех разрядов, вплоть до LSB. В конце цикла преобразования вырабатывается сигнал EOC, преобразование завершается, данные из регистра SAR могут быть считаны внешней логикой. Временная диаграмма цикла преобразования приведена на рисунке 70. Вместе со сбросом/установкой и циклом записи данных в УВХ преобразование занимает 40 тактов сигнала CLK (12 тактов записи данных в УВХ и 28 тактов собственно преобразование). Поэтому для обеспечения частоты сэмплирования 0.8МГц требуется входной тактовый сигнал частотой не менее 32МГц. Для корректной работы входного мультиплексора данные дешифратора выбора соответствующего входа данных записываются во внутренний регистр адреса по завершении двух из 28 внутренних тактов преобразования. Таким образом, в SAH данные по новому входу записываются в начале следующего цикла преобразования, позволяя завершить текущий. Сигнал Start должен подаваться на АЦП и защёлкиваться по переднему фронту CLK. При этом его длительность должна быть не менее 12 тактов CLK при заданных параметрах входа данных.

Считывание цифровых данных осуществляется по заднему фронту CLK в такте C1_27 или по переднему фронту CLK в такте C0_0 следующего цикла конвертации при активной «1» на выходе EOC.

В общем случае сигнал EOC формируется по переднему фронту CLK с задержкой порядка 8ns и имеет длительность порядка 2/Fclk. Активный уровень сигнала EOC на выходе блока всегда заканчивается позже переднего фронта сигнала CLK, при этом данное соотношение не гарантируется вне блока.

Для управления АЦП используются регистры блока управления аналоговой подсистемой. Состав регистров управления АЦП представлен в таблице 146.

Регистры

Список регистров

| Обозначение | Смещение | Начальное значение | Назначение | Доступ |

| ADC_CONFIG | 0x3C | 0x0 | Регистр настроек | RW |

| ADC_CONTINUOUS | 0x40 | 0x0 | Управление непрерывным измерением | RW |

| ADC_SINGLE | 0x44 | 0x0 | Управление однократным измерением | WO |

| ADC_VALID | 0x48 | 0x0 | Регистр статуса | RО |

| ADC_VALUE | 0x4C | 0x0 | Регистр данных | RО |

| REF_CLB | 0x38 | 0x01 | Управление калибруемыми источниками тока и напряжения | RW |

Описание регистров

ADC_CONFIG

Смещение: 0x3C - регистр настроек. Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| зарезервировано | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Зарезервировано | Sel | Ext_Clb | ExtRef | Rn | EN | ||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 6:4 Sel - Выбор канала АЦП

Бит 3 Ext_Clb - Выбор источника внешнего опорного напряжения:

- 1 - внешний вывод;

- 0 - настраиваемый ОИН.

Бит 2 ExtRef - Выбор источника опорного напряжения:

- 1 - внешний;

- 0 - встроенный

Бит 1 Rn - Бит сброса АЦП, активный уровень «0»

Бит 0 EN - Управление питанием АЦП:

- 0 - выключен;

- 1 - включен

ADC_ CONTINUOUS

Смещение: 0x40 - регистр управления непрерывным измерением. Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Зарезервировано | Continuous | ||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Бит 0 Continuous - Запуск / остановка непрерывного измерения

- 1 - запуск непрерывного преобразования

- 0 - остановка непрерывного преобразования

ADC_ SINGLE

Смещение: 0x44 - регистр управления непрерывным измерением. Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Зарезервировано | Single | ||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Бит 0 Single - Запуск однократного измерения

- 1 - запуск однократного преобразования

- 0 - остановка однократного преобразования

ADC_ VALID

Смещение: 0x48 - регистр управления непрерывным измерением. Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Зарезервировано | Valid | ||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ro |

Бит 0 Valid - Признак наличия актуальных данных

- 1 - данные готовы

- 0 - преобразование не завершено

ADC_ VALUE

Смещение: 0x4С - регистр данных. Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| ro | ro | ro | ro | ro | ro | ro | ro | ro | ro | ro | ro | ro | ro | ro | ro |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Зарезервировано | Data | ||||||||||||||

| ro | ro | ro | ro | ro | ro | ro | ro | ro | ro | ro | ro | ro | ro | ro | ro |

Биты 11:0 Data - 12-битный результат преобразования