Ускоритель CRC

Общее описание

Блок предназначен для вычисления циклической контрольной суммы (CRC) массива данных без использования вычислительных ресурсов центрального процессора.

Инструкции работы с блоком

Введение

Блок вычисления контрольных сумм находится на шине AHP и доступен по очереди с APB_P и Ускорителем криптографии.

Описание модуля CRC

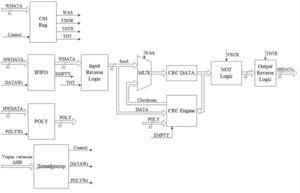

Контроллер состоит из следующих компонентов:

- дешифратора системных сигналов шины AHB,

- регистра управления CtrlReg,

- регистра полинома POLY Reg,

- входного буфера IFIFO объемом 16 слов по 32 бита,

- логики перестановки битов входных данных Input Reverse Logic,

- устройства кодирования CRC_Engine с мультиплексором MUX и сдвиговым регистром CRC DATA,

- логики инверсии NOT Logic и логики перестановки битов выходных данных Output Reverse Logic.

Дешифратор системных сигналов формирует сигналы чтения и записи всех регистров контроллера в соответствии с адресным пространством. Регистр управления CtrlReg управляет всеми настройками процесса вычисления суммы. Регистр полинома POLY Reg предназначен для хранения значения полинома. Входной буфер IFIFO осуществляет буферизацию входных данных, по которым будет считаться контрольная сумма. Этот буфер, а также регистры управления и полинома подключены напрямую к шине HWDATA. При полном заполнении буфера активизируется сигнал HREADY_o, останавливающий транзакцию по шине AHB. Логика перестановки битов входных данных предназначена для перестановки битов и байтов слова входных данных и управляется битами поля TOT регистра управления. Устройство кодирования CRC_Engine с мультиплексором MUX и сдвиговым регистром CRC DATA производят вычисление контрольной суммы последовательности входных данных. Вычисленная контрольная сумма записывается в выходной регистр логики перестановки битов выходных данных Output Reverse Logic через логику инверсии NOT Logic, которая инвертирует или не инвертирует выходные данные в зависимости от значения бита FXOR регистра управления. Логика перестановки битов выходных данных предназначена для перестановки битов и байтов слова вычисленной контрольной суммы и управляется битами поля TOTR регистра управления. Выходные биты контрольной суммы подключены напрямую к шине HRDATA.

Порядок работы с блоком CRC

Для вычисления контрольной суммы необходимо выполнить следующую последовательность действий:

- установить необходимые значения битов перестановки и инверсии (поля TOT, TOTR и FXOR);

- записать в регистр полинома требуемое 32-разрядное значение полинома;

- установить в единицу бит WAS регистра управления;

- записать в регистр данных 32-разрядное начальное значение;

- сбросить в ноль бит WAS регистра управления;

- записать необходимое количество данных в регистр данных;

- прочитать из регистра данных вычисленное значение контрольной суммы.

Описание регистров

Карта регистров блока приведена в таблице ниже. Запись данных в регистр данных может осуществляться в 8, 16 или 32-разрядном режиме. Доступ к остальным регистрам осуществляется только в 32-разрядном режиме.

Регистр DATA

Смещение: 0x0, Значение после подачи сброса: 0x????????;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| DATA[31:0] | |||||||||||||||||||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 31:0 DATA[31:0] - Регистр данных

При записи в этот регистр назначение принимаемых данных различное и определяется значением бита WAS регистра управления модуля: если этот бит равен 1, то записанное в регистр данных 32-разрядное значение является начальным значением контрольной суммы, если бит WAS равен нулю, то пишутся обычные данные.

Регистр данных при чтении выдает содержимое регистра вычисленной контрольной суммы.

Регистр POLY

Смещение: 0x4, Значение после подачи сброса: 0x????????;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| POLY[31:0] | |||||||||||||||||||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 31:0 POLY[31:0] - Регистр полинома служит для хранения значения полинома, по которому будет считаться контрольная сумма.

При записи в этот регистр назначается новый рабочий полином

При чтении выдается рабочий полином

Регистр CTRL

Смещение: 0x08, Значение после подачи сброса: 0x????????;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| TOT | TOTR | reserved | FXOR | WAS | reserved | ||||||||||

| rw | rw | rw | rw | - | rw | rw | - | - | - | - | - | - | - | - | - |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| reserved | Busy | ||||||||||||||

| - | - | - | - | - | - | - | - | - | - | - | - | - | - | - | r |

Биты 31:30 TOT[1:0] - Перестановка битов/байтов входных данных:

- 00 – перестановка выключена;

- 01 – биты в байтах перестанавливаются (бит 7 с битом 0, бит 15 с битом 8, с остальными байтами так же), байты НЕ перестанавливаются;

- 10 – перестанавливаются и биты, и байты

- 11 – биты в байтах НЕ перестанавливаются, байты перестанавливаются (меняются местами байты 3 и 0, 2 и 1);

Биты 29:28 TOTR[1:0] - Перестановки битов/байтов выходных данных:

- 00 – перестановка выключена;

- 01 – биты в байтах перестанавливаются (бит 7 с битом 0, бит 6 с битом 1 и т.д.; бит 15 c битом 8, бит 14 с битом 9 и т.д., с остальными байтами так же), байты НЕ перестанавливаются;

- 10 – перестанавливаются и биты, и байты

- 11 – биты в байтах НЕ перестанавливаются, байты перестанавливаются (меняются местами байты 3 и 0, 2 и 1);

Бит 26 FOXR - Инверсия контрольной суммы.

Некоторые протоколы подсчета контрольной суммы требуют инверсии вычисленного значения контрольной суммы (выполняется операция XOR со значением 0xFFFFFFFF):

- 0 – инверсия выключена;

- 1 – инверсия включена (операция XOR выполняется)

Бит 25 WAS - Назначение регистра данных:

- 0 – записываем данные;

- 1 – записываем начальное значение

Бит 0 Busy- Бит занятости автомата:

- 0 – автомат закончил вычисления;

- 1 – автомат занят.После записи в регистр данных слова для вычисления контрольной суммы бит занятости перейдет в состояние единицы через один такт после такта записи. То есть чтение регистра управления, идущее на шине AHB сразу на следующем такте после записи данных, вернет результат с нулевым (еще не обновленным) значением бита Busy