Процессор: различия между версиями

Материал из MIK32 микроконтроллер

Нет описания правки |

Нет описания правки |

||

| Строка 1: | Строка 1: | ||

В состав микросхемы | В состав микросхемы входит ядро '''SCR1''', разработка компании '''Syntacore''', на базе открытой архитектуры RISC-V. | ||

Реализована следующая конфигурация: | Реализована следующая конфигурация: | ||

Текущая версия от 16:02, 6 апреля 2023

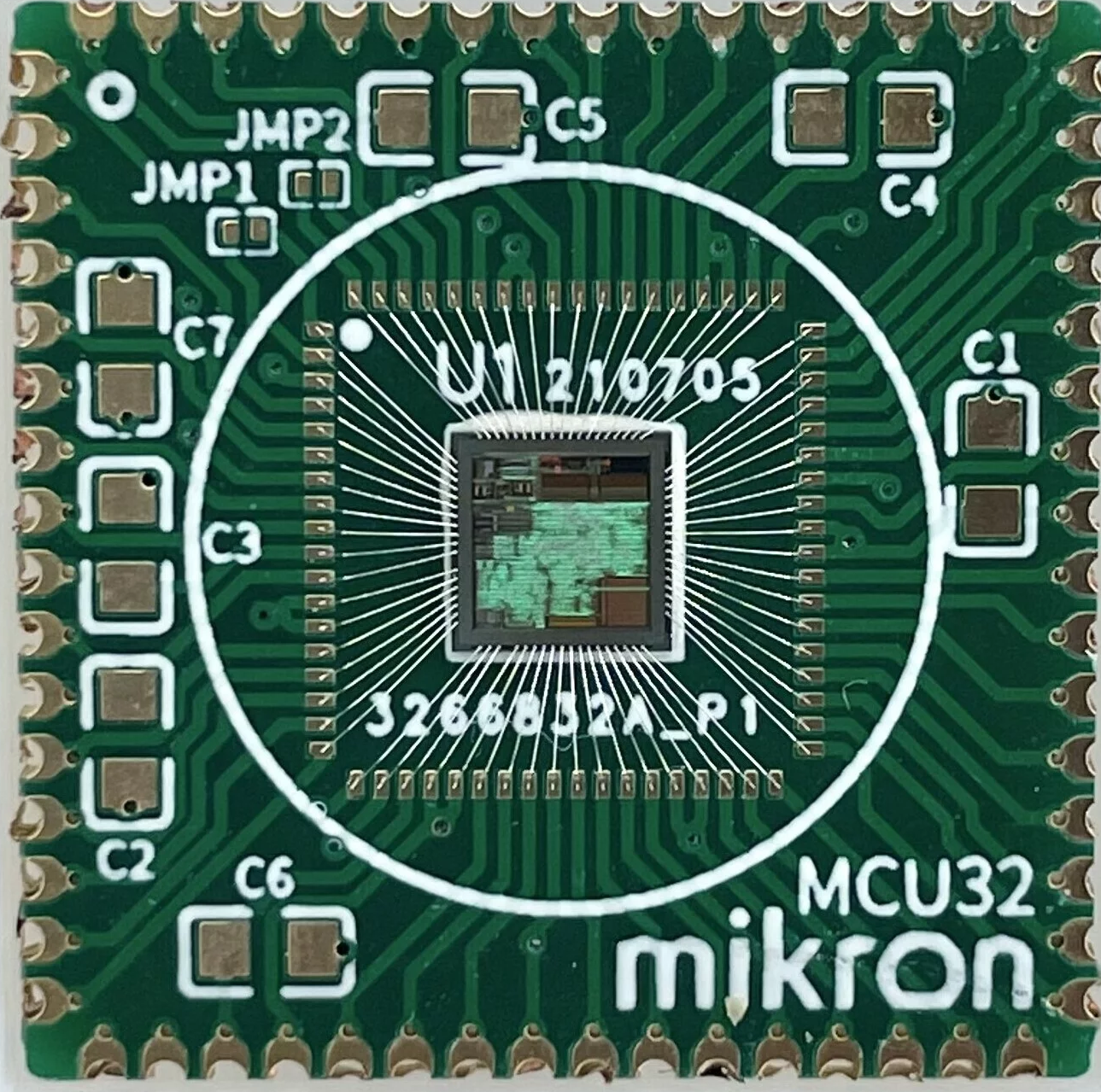

В состав микросхемы входит ядро SCR1, разработка компании Syntacore, на базе открытой архитектуры RISC-V.

Реализована следующая конфигурация:

- RV32I - базовый целочисленный набор команд (минимальный необходимый набор команд, 32х-битное адресное пространство, 32 регистра общего назначения по 32 бита, все инструкции ширины 32 бита);

- расширение «M» - стандартное опциональное расширение для операций целочисленного умножения и деления;

- расширение «С» - стандартное опциональное расширение для сокращенных инструкций, дополнительный набор инструкций ширины 16 бит;

- встроенный интегрированный программируемый контроллер прерываний отключен;

- поддержка отладки через интерфейс JTAG IEEE Std 1149.1-2013 (совместима с RISC-V External Debug Support Spec Ver. 0.13.2), поддержка стандартных функций отладки: Reset, Halt / Resume / Step, доступ к GPR, CSR, MEM, HW Breakpoint / Watchpoint;

- трехстадийный конвейер;