Управление тактированием: различия между версиями

(Новая страница: « '''Схема тактирования''' мини|894x894пкс Тактовые импульсы можно подавать двумя способами: внутренней и внешний генератор Существует несколько типов тактовых резонаторов: # RC-цепи # Керамичсекие резонаторы # Кварцевые резон...») |

(Добавлена таблица 2) |

||

| Строка 48: | Строка 48: | ||

Описание полей регистров модуля PM для управления так- тированием представлено в таблице 2. | Описание полей регистров модуля PM для управления так- тированием представлено в таблице 2. | ||

'''Таблица 1. Регистры и поля управления тактированием модуля WU''' | |||

{| class="wikitable" | {| class="wikitable" | ||

| Строка 108: | Строка 110: | ||

|[14] | |[14] | ||

|Режим повышенного потребления, активный уровень “0” для OSC32K | |Режим повышенного потребления, активный уровень “0” для OSC32K | ||

|} | |||

'''Таблица 2. Регистры управления тактированием модуля PM''' | |||

{| class="wikitable" | |||

|+ | |||

!Регистр | |||

!Смешение | |||

!Обозначение | |||

!Номер разряда | |||

!Описание | |||

|- | |||

|DIV_AHB | |||

|0x00 | |||

|DIV_AHB | |||

|[7:0] | |||

|Делитель частоты AHB | |||

|- | |||

|DIV_APB_M | |||

|0x04 | |||

|DIV_APB_M | |||

|[7:0] | |||

|Делитель частоты APB_M | |||

|- | |||

|DIV_APB_P | |||

|0x08 | |||

|DIV_APB_P | |||

|[7:0] | |||

|Делитель частоты APB_P | |||

|- | |||

| rowspan="2" |AHB_MUX | |||

| rowspan="2" |0x24 | |||

|AHB_CLK_MUX | |||

|[1:0] | |||

|Выбор источника тактирования системы: | |||

0 – внешний OSC32M; | |||

1 – внутренний OSC32M; | |||

2 – внешний OSC32K; | |||

3 – внутренний OSC32К | |||

|- | |||

|FORCE_MUX | |||

|[3] | |||

|Запрет на принудительное переключение с выбранеого источника тактирования при пропадании тактирования | |||

|- | |||

|WDT_CLK_MUX | |||

|0x28 | |||

|WDT_CLK_MUX | |||

|[1:0] | |||

|Выбор источника тактирования сторожевого таймера: | |||

0 – внешний OSC32M; | |||

1 – внутренний HSI32M; | |||

2 – внешний OSC32K; | |||

3 – внутренний LSI32К; | |||

|- | |||

|CLK_AHB_SET | |||

CLK_AHB_CLEAR | |||

|0x0C | |||

0x10 | |||

|CLK_AHB_SET | |||

CLK_AHB_CLEAR | |||

|[7:0] | |||

|Управление тактированием устройств на шине AHB. | |||

Запись «1» в CLK_AHB_SET включает тактирования, запись «1» в CLK_AHB_CLEAR отключает тактирование. Каждому биту соответствует одно устройство: | |||

0 – Ядро; | |||

1 – RAM; | |||

2 – EEPROm; | |||

3 – SPIFI; | |||

4 – DMA; | |||

5 – TCB; | |||

6 – ускоритель криптографии; | |||

7 – CRC32 | |||

|- | |||

|CLK_APB_M_SET | |||

CLK_APB_M_CLEAR | |||

|0x14 | |||

0x18 | |||

|CLK_APB_M_SET | |||

CLK_APB_M_CLEAR | |||

|[8:0] | |||

|Управление тактированием устройств на шине APB_M. | |||

Запись «1» в Clk_ APBm_Set включает тактирование, запись «1» в CLK_APB_M_CLEAR отключает тактирование. | |||

Каждому биту соответствует одно устройство: | |||

0 – Блок управления питанием (PM - Power Monitor); | |||

1 – контроллер прерываний; | |||

2 – таймер32_0; | |||

3 – контроллер выводов; | |||

4 – Сторожевой таймер шины | |||

5 – OTP; | |||

6 – монитор питания системного домена | |||

7 – блок WU батарейного домена | |||

8 – RTC батарейного домена | |||

|- | |||

|CLK_APB_P_SET | |||

CLK_APB_P_CLEAR | |||

|0x1C | |||

0x20 | |||

|CLK_APB_P_SET | |||

CLK_APB_P_CLEAR | |||

|[16:0] | |||

|Управление тактированием устройств на шине APB_P. | |||

Запись «1» в Clk_ APBp_Set включает тактирование, запись «1» в CLK_APB_P_CLEAR отключает тактирование. | |||

Каждому биту соответствует одно устройство: | |||

0 – сторожевой таймер; | |||

1 – UART_0; | |||

2 – UART_1; | |||

3 – таймер16_0; | |||

4 – таймер16_1; | |||

5 – таймер16_2; | |||

6 – таймер32_1; | |||

7 – таймер32_2; | |||

8 – SPI_0; | |||

9 – SPI_1; | |||

10 – I2C_0; | |||

11 – I2C_1; | |||

12 – GPIO_0; | |||

13 – GPIO_1; | |||

14 – GPIO_2; | |||

15 – регистры аналоговых блоков; | |||

16 – схема формирования прерываний GPIO | |||

|} | |} | ||

Версия от 11:42, 16 июля 2024

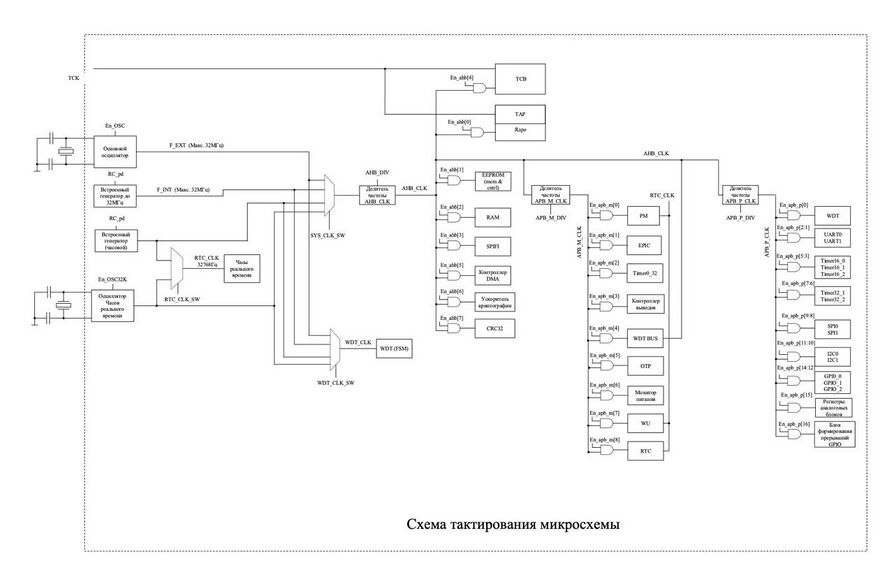

Схема тактирования

Тактовые импульсы можно подавать двумя способами: внутренней и внешний генератор Существует несколько типов тактовых резонаторов:

- RC-цепи

- Керамичсекие резонаторы

- Кварцевые резонаторы

Микроконтроллер MIK32 оснащен четырьмя генераторами, два на основе внешнего кварцевого резонатора и два на встроенном контуре RC.

- Внешние генераторы

- OSC32K – генератор с выводами для подключения внешнего часового кварцевого резонатора;

- OSC32M – генератор с выводами для подключения внешнего кварцевого резонатора для тактирования системы с частотой от 1 до 32 МГц (генератор по-умолчанию);

- Внутренние генераторы

- HSI32M – встроенный генератор с частотой 32 МГц с возможностью корректировки частоты;

- LSI32K встроенных генератора с частотой 32 кГц с возможностью корректировки частоты;

- монитор частоты, предназначен для контроля состояния источников тактирования во время работы микроконтроллера;

Управление тактированием

Для выбора источников тактирования, задания делителей частоты, управлением HSI32M и OSC32M используются регистры модулей PowerManager и WakeUp.

Для управления тактированием часов реального времени и управлением LSI32K и OSC32K используются регистра модуля WakeUp. При включении питания и по внешнему сбросу:

- тактирование осуществляется от внешнего осциллятора 32 МГц (OSC32M);

- значения делителей шин AHB, APB_M, APB_P равны 0, то есть указанные шины работают на частоте осциллятора;

- тактирование RAM, EEPROM, SPIFI, PowerManager, WakeUp включено, так- тирование остальных устройств выключено;

- тактирование сторожевого таймера осуществляется от встроенного осцилля- тора 32 МГц;

- внешние осцилляторы OSC32K и OSC32M включены. Перед использованием внешнего осциллятора его необходимо включить записью «0» в поле OCS32M;

Перед использованием внешнего осциллятора его необходимо включить запи- сью «0» в поле OCS32M_en регистра Generator блока WakeUp.

При необходимости, для снижения потребления встроенный осциллятор 32 MГц выключен путем записи «1» в поле RC32M_en регистра Generator блока PM.

Для подстройки встроенного осциллятора HSI32M используются поправочные коэффициент с допустимым значением от 0 до 255.

Для подстройки встроенного осциллятора LSI32K используются поправочные коэффициент с допустимым значением от 0 до 255.

Описание полей регистров модуля WU для управления тактированием пред- ставлено в таблице 1.

Описание полей регистров модуля PM для управления так- тированием представлено в таблице 2.

Таблица 1. Регистры и поля управления тактированием модуля WU

| Регистр | Смешение | Обозначение | Номер разряда | Описание |

|---|---|---|---|---|

| CLOCKS_SYS | 0х14 | OSC32M_EN | [0] | Включение/отключение внешнего осцилятора

0 – включение; 1 – отключение |

| HSI32M_EN | [1] | Включение/отключение HSI32M

0 – включение; 1 – отключение | ||

| ADJ_HSI32M | [9:2] | Поправочные коэффициенты HSI32M | ||

| FORCE_32K_CLK | [11:10] | Принудительное переклю- чение на опорный источник для монитора частоты

2’b01 – принудительно выбран OSC32K 2’b10 – принудительно выбран LSI32K | ||

| CLOCKS_BU | 0х10 | OSC32K_EN | [0] | Включение/отключение внешнего осцилятора на 32 KГц

0 – включение; 1 – отключение |

| LSI32K_EN | [1] | Включение/отключение LSI32К

0 – включение; 1 – отключение | ||

| ADJ_LSI32K | [9:6] | Поправочные коэффициенты LSI32К | ||

| RTC_CLK_MUX | [11:10] | Выбор источника тактирования часов реального времени:

0x1 – внутренний LSI32К; 1x2 – внешний осциллятор OSC32K | ||

| OSC32K_SM | [14] | Режим повышенного потребления, активный уровень “0” для OSC32K |

Таблица 2. Регистры управления тактированием модуля PM

| Регистр | Смешение | Обозначение | Номер разряда | Описание |

|---|---|---|---|---|

| DIV_AHB | 0x00 | DIV_AHB | [7:0] | Делитель частоты AHB |

| DIV_APB_M | 0x04 | DIV_APB_M | [7:0] | Делитель частоты APB_M |

| DIV_APB_P | 0x08 | DIV_APB_P | [7:0] | Делитель частоты APB_P |

| AHB_MUX | 0x24 | AHB_CLK_MUX | [1:0] | Выбор источника тактирования системы:

0 – внешний OSC32M; 1 – внутренний OSC32M; 2 – внешний OSC32K; 3 – внутренний OSC32К |

| FORCE_MUX | [3] | Запрет на принудительное переключение с выбранеого источника тактирования при пропадании тактирования | ||

| WDT_CLK_MUX | 0x28 | WDT_CLK_MUX | [1:0] | Выбор источника тактирования сторожевого таймера:

0 – внешний OSC32M; 1 – внутренний HSI32M; 2 – внешний OSC32K; 3 – внутренний LSI32К; |

| CLK_AHB_SET

CLK_AHB_CLEAR |

0x0C

0x10 |

CLK_AHB_SET

CLK_AHB_CLEAR |

[7:0] | Управление тактированием устройств на шине AHB.

Запись «1» в CLK_AHB_SET включает тактирования, запись «1» в CLK_AHB_CLEAR отключает тактирование. Каждому биту соответствует одно устройство: 0 – Ядро; 1 – RAM; 2 – EEPROm; 3 – SPIFI; 4 – DMA; 5 – TCB; 6 – ускоритель криптографии; 7 – CRC32 |

| CLK_APB_M_SET

CLK_APB_M_CLEAR |

0x14

0x18 |

CLK_APB_M_SET

CLK_APB_M_CLEAR |

[8:0] | Управление тактированием устройств на шине APB_M.

Запись «1» в Clk_ APBm_Set включает тактирование, запись «1» в CLK_APB_M_CLEAR отключает тактирование. Каждому биту соответствует одно устройство: 0 – Блок управления питанием (PM - Power Monitor); 1 – контроллер прерываний; 2 – таймер32_0; 3 – контроллер выводов; 4 – Сторожевой таймер шины 5 – OTP; 6 – монитор питания системного домена 7 – блок WU батарейного домена 8 – RTC батарейного домена |

| CLK_APB_P_SET

CLK_APB_P_CLEAR |

0x1C

0x20 |

CLK_APB_P_SET

CLK_APB_P_CLEAR |

[16:0] | Управление тактированием устройств на шине APB_P.

Запись «1» в Clk_ APBp_Set включает тактирование, запись «1» в CLK_APB_P_CLEAR отключает тактирование. Каждому биту соответствует одно устройство: 0 – сторожевой таймер; 1 – UART_0; 2 – UART_1; 3 – таймер16_0; 4 – таймер16_1; 5 – таймер16_2; 6 – таймер32_1; 7 – таймер32_2; 8 – SPI_0; 9 – SPI_1; 10 – I2C_0; 11 – I2C_1; 12 – GPIO_0; 13 – GPIO_1; 14 – GPIO_2; 15 – регистры аналоговых блоков; 16 – схема формирования прерываний GPIO |