Порты ввода вывода GPIO

Общая информация

Каждая линия любого порта может быть независимо от остальных выводов сконфигурирована как вход или как выход и управляться через регистры состояния. Если линия порта работает как вход, то можно считать её состояние из регистра статуса. Если линия порта работает как выход, то можно перевести её значение в состояние логического 0 или 1 записью в выходной регистр.

Выводы, помимо функции программного управления, могут управляться периферийными блоками, а так же иметь аналоговый функционал (ЦАП/АЦП).

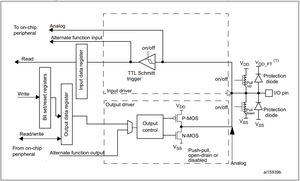

Типовая структура порта представлена на следующей функциональной схеме. Каждый вывод снабжен так же встроенными отключаемыми подтяжками к Vdd и Vss.

Режим "открытый сток" не реализован.

Программное управление выводами

Введение

Каждый модуль ввода/вывода (GPIO) подключен к шине APB и управляет до 16 внешними выводами. Каждый из внешних выводов может управляться индивидуально.

Для работы с конфигурационными регистрами и операционными регистрами требуется подать тактовый сигнал на эти блоки.

Регистры

Далее перечислены регистры модуля GPIO. Все регистры имеют разрядность соответствующую количествам выводов блока.

Регистр GPIOx_SET_STATUS

Смещение: 0x00, Значение после подачи сброса: 0x0000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SS15 | SS14 | SS13 | SS12 | SS11 | SS10 | SS9 | SS8 | SS7 | SS6 | SS5 | SS4 | SS3 | SS2 | SS1 | SS0 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 31:16 Зарезервировано

Биты 15:0 SSy - Биты установки порта в 1цу (y=0...15)

При записи:

- 0: эффекта нет

- 1: соответствующий вывод y порта x будет переведен в состояние логической 1

При чтении - состояние вывода y порта x.

Регистр GPIOx_RESET

Смещение: 0x04, Значение после подачи сброса: 0x0000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| OR15 | OR14 | OR13 | OR12 | OR11 | OR10 | OR9 | ORR8 | OR7 | OR6 | OR5 | OR4 | OR3 | OR2 | OR1 | OR0 |

| w | w | w | w | w | w | w | w | w | w | w | w | w | w | w | w |

Биты 31:16 Зарезервировано

Биты 15:0 ORy - Биты установки порта в 0 (y=0...15)

При записи:

- 0: эффекта нет

- 1: соответствующий вывод y порта x будет переведен в состояние логического 0

Регистр GPIOx_SET_DIRECTION_OUT

Смещение: 0x08, Значение после подачи сброса: 0x0000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| DIR15 | DIR14 | DIR13 | DIR12 | DIR11 | DIR10 | DIR9 | DIR8 | DIR7 | DIR6 | DIR5 | DIR4 | DIR3 | DIR2 | DIR1 | DIR0 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 31:16 Зарезервировано

Биты 15:0 DIRy - Биты установки порта в 0 (y=0...15)

При записи:

- 0: эффекта нет

- 1: соответствующий вывод y порта x будет переведен в состояние выхода

При чтении текущая конфигурация вывода y порта х

- 0: вывод в режиме выхода

- 1: вывод в режиме входа

Регистр GPIOx_SET_DIRECTION_IN

Смещение: 0x0C, Значение после подачи сброса: 0x0000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| DIR15 | DIR14 | DIR13 | DIR12 | DIR11 | DIR10 | DIR9 | DIR8 | DIR7 | DIR6 | DIR5 | DIR4 | DIR3 | DIR2 | DIR1 | DIR0 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 31:16 Зарезервировано

Биты 15:0 DIRy - Биты установки порта в 0 (y=0...15)

При записи:

- 0: эффекта нет

- 1: соответствующий вывод y порта x будет переведен в состояние выхода

При чтении текущая конфигурация вывода y порта х

- 0: вывод в режиме выхода

- 1: вывод в режиме входа

Регистр GPIOx_OUTPUT

Смещение: 0x10, Значение после подачи сброса: 0x0000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| OD15 | OD14 | OD13 | OD12 | OD11 | OD10 | OD9 | OD8 | OD7 | OD6 | OD5 | OD4 | OD3 | OD2 | OD1 | OD0 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 31:16 Зарезервировано

Биты 15:0 ODy - Биты установки порта в 0 (y=0...15)

При записи:

- 0: соответствующий вывод y порта x будет переведен в состояние 0

- 1: соответствующий вывод y порта x будет переведен в состояние 1

При чтении текущее состояние вывода y порта х

- 0: вывод в 0

- 1: вывод в 1

Дополнительный/альтернативный функционал выводов

Введение

Помимо основной функции программного управления входы-выходы GPIO мультиплексированы с входами-выходами встроенных периферийных модулей. Назначение и схема мультеплексирования представлена в таблице выводов. Для управления функциями используются регистры конфигурации.

Ячейка ввода-вывода позволяет регулировать нагрузочную способность вывода с помощью специального регистра

А так же можно подключать резисторы подтяжки к питанию/земле активируя соответствующую функцию в соответствующем специальном регистре

Регистры

Далее перечислены регистры модуля PAD. Все регистры имеют разрядность соответствующую удвоенному количеству выводов соответствующего порта (32 или 16).

Регистр PADx_CFG

Смещение: 0x00 + x*4, Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| CFG15 | CFG14 | CFG13 | CFG12 | CFG11 | CFG10 | CFG9 | CFG8 | ||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CFG7 | CFG6 | CFG5 | CFG4 | CFG3 | CFG2 | CFG1 | CFG0 | ||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 2y:2y+1: CFGy[0:1]: конфигурация вывода y, порта x:

- 00 – первая функция (последовательный интерфейс)

- 01 – вторая функция (порт о,щего назначения)

- 10 – третья функция (последовательный интерфейс или таймер)

- 11 – четвертая функция (аналоговый сигнал)

При записи меняет режим порта в выбранное состояние

При чтении - текущая конфигурация выводов порта

Регистр PADx_DS

Смещение: 0x0С + x*4, Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| DS15 | DS14 | DS13 | DS12 | DS11 | DS10 | DS9 | DS8 | ||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| DS7 | DS6 | DS5 | DS4 | DS3 | DS2 | DS1 | DS0 | ||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 2y:2y+1: DSy[0:1]: конфигурация вывода y, порта x:

- 00 – 2мА

- 01 – 4мА

- 10 – 8мА

- 11 – 8мА

При записи меняет режим порта в выбранное состояние

При чтении - текущая конфигурация выводов порта

Регистр PADx_PUPD

Смещение: 0x18 + x*4, Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| PUPD15 | PUPD14 | PUPD13 | PUPD12 | PUPD11 | PUPD10 | PUPD9 | PUPD8 | ||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| PUPD7 | PUPD6 | PUPD5 | PUPD4 | PUPD3 | PUPD2 | PUPD1 | PUPD0 | ||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 2y:2y+1: PUPDy[0:1]: конфигурация вывода y, порта x:

- 00 – регистры подтяжки не подключаются

- 01 – подключен регистр подтяжки к питанию

- 10 – подключен регистр подтяжки к земле

- 11 – зарезервировано

При записи меняет режим порта в выбранное состояние

При чтении - текущая конфигурация выводов порта