Порты ввода вывода GPIO: различия между версиями

мНет описания правки |

м (→Регистры) |

||

| Строка 94: | Строка 94: | ||

При чтении - состояние вывода y порта x. | При чтении - состояние вывода y порта x. | ||

==== Регистр GPIOx_CLEAR ==== | |||

Cмещение: 0x04, Значение после подачи сброса: 0x0000; | |||

{| class="wikitable" | |||

|31 | |||

|30 | |||

|29 | |||

|28 | |||

|27 | |||

|26 | |||

|25 | |||

|24 | |||

|23 | |||

|22 | |||

|21 | |||

|20 | |||

|19 | |||

|18 | |||

|17 | |||

|16 | |||

|- | |||

| colspan="16" |Зарезервировано | |||

|} | |||

{| class="wikitable" | |||

|15 | |||

|14 | |||

|13 | |||

|12 | |||

|11 | |||

|10 | |||

|9 | |||

|8 | |||

|7 | |||

|6 | |||

|5 | |||

|4 | |||

|3 | |||

|2 | |||

|1 | |||

|0 | |||

|- | |||

|ORR15 | |||

|ORR14 | |||

|ORR13 | |||

|ORR12 | |||

|ORR11 | |||

|ORR10 | |||

|ORR9 | |||

|ORR8 | |||

|ORR7 | |||

|ORR6 | |||

|ORR5 | |||

|ORR4 | |||

|ORR3 | |||

|ORR2 | |||

|ORR1 | |||

|ORR0 | |||

|- | |||

|w | |||

|w | |||

|w | |||

|w | |||

|w | |||

|w | |||

|w | |||

|w | |||

|w | |||

|w | |||

|w | |||

|w | |||

|w | |||

|w | |||

|w | |||

|w | |||

|} | |||

Биты 31:16 Зарезервировано | |||

Биты 15:0 OSRy - Биты установки порта в 0 (y=0...15) | |||

При записи: | |||

* 0: эффекта нет | |||

* 1: соответствующий вывод y порта x будет переведен в состояние логического 0 | |||

Версия от 14:14, 7 апреля 2023

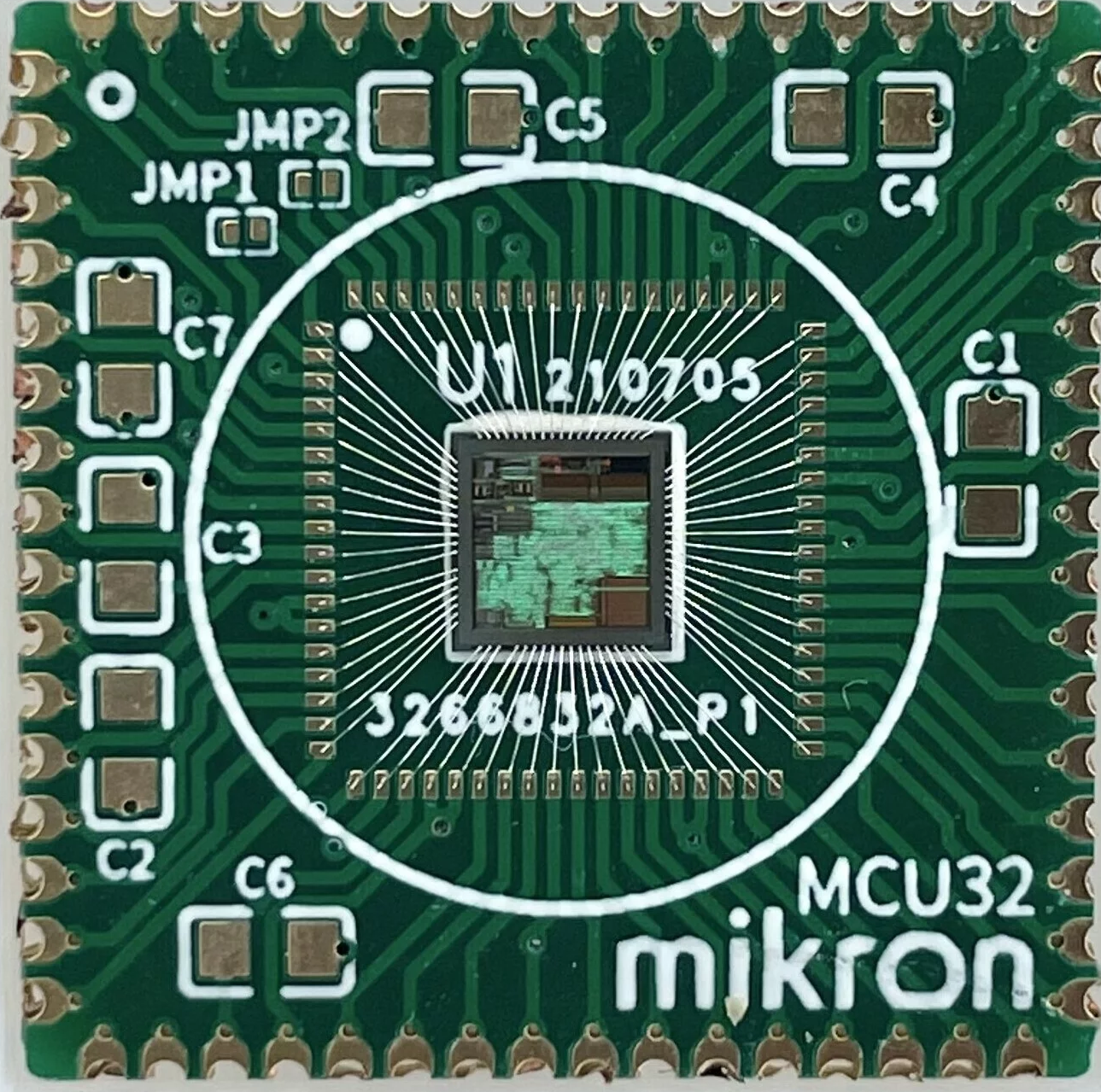

Общая информация

Каждый модуль ввода/вывода (GPIO) подключен к шине APB и управляет до 16 внешними выводами. Каждый из внешних выводов может управляться индивидуально.

Каждый вывод снабжен встроенными отключаемыми подтяжками к Vdd и Vss.

Выводы помимо функции программного управления так же могут управляться периферийными блоками, а так же иметь аналоговый функционал (ЦАП/АЦП)

Регистры

В таблице перечислены регистры модуля GPIO. Все регистры имеют разрядность соответствующую количествам выводов блока.

Регистр GPIOx_SET / GPIOx_STATUS

Cмещение: 0x00, Значение после подачи сброса: 0x0000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| OSR15 | OSR14 | OSR13 | OSR12 | OSR11 | OSR10 | OSR9 | OSR8 | OSR7 | OSR6 | OSR5 | OSR4 | OSR3 | OSR2 | OSR1 | OSR0 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 31:16 Зарезервировано

Биты 15:0 OSRy - Биты установки порта в 1цу (y=0...15)

При записи:

- 0: эффекта нет

- 1: соответствующий вывод y порта x будет переведен в состояние логической 1

При чтении - состояние вывода y порта x.

Регистр GPIOx_CLEAR

Cмещение: 0x04, Значение после подачи сброса: 0x0000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ORR15 | ORR14 | ORR13 | ORR12 | ORR11 | ORR10 | ORR9 | ORR8 | ORR7 | ORR6 | ORR5 | ORR4 | ORR3 | ORR2 | ORR1 | ORR0 |

| w | w | w | w | w | w | w | w | w | w | w | w | w | w | w | w |

Биты 31:16 Зарезервировано

Биты 15:0 OSRy - Биты установки порта в 0 (y=0...15)

При записи:

- 0: эффекта нет

- 1: соответствующий вывод y порта x будет переведен в состояние логического 0