Процессор, память и архитектура шин

Материал из MIK32 микроконтроллер

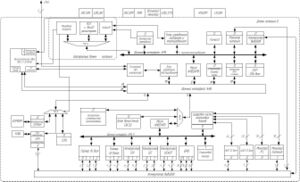

Архитектура шин

Блок схема представляет внутреннюю коммуникацию основных блоков микроконтроллера.

Сторожевой таймер шины, контролирует время отклика ведомых устройств на шине AHB (контроллер EEPROM, CRC32, ускоритель симметричной криптографии).

Процессорная часть

В состав микросхемы входит ядро SCR1, разработка компании Syntacore, на базе открытой архитектуры RISC-V.

Реализована следующая конфигурация:

- Процессорное ядро RV32I - базовый целочисленный набор команд (минимальный необходимый набор команд, 32х-битное адресное пространство, 32 регистра общего назначения по 32 бита, все инструкции ширины 32 бита);

- расширение «M» - стандартное опциональное расширение для операций целочисленного умножения и деления;

- расширение «С» - стандартное опциональное расширение для сокращенных инструкций, дополнительный набор инструкций ширины 16 бит;

- встроенный интегрированный программируемый контроллер прерываний отключен;

- поддержка отладки через интерфейс JTAG IEEE Std 1149.1-2013 (совместима с RISC-V External Debug Support Spec Ver. 0.13.2), поддержка стандартных функций отладки: Reset, Halt / Resume / Step, доступ к GPR, CSR, MEM, HW Breakpoint / Watchpoint;

- трехступенчатый конвейер;

- матрица AHB, обеспечивает коммутацию всех устройств с интерфейсами AHB и APB.

- системный TAP контроллер, обеспечивает доступ к отладочному тестовому интерфейсу, обеспечивает граничное сканирование выводов микросхемы;

- блок управления тестированием, предназначен для управления тестированием памяти и аналоговых блоков, а также обеспечивает доступ к регистрам периферийных модулей и ячейкам памяти без участия ядра;

Память

- Статическое ОЗУ размером 4096x32 с поддержкой байтового доступа;

- блок однократно программируемой памяти ПЗУ размером 256 бит с возможностью программного чтения данных, предназначен для хранения поправочных коэффициентов и заводского номера изделия;

- блок электрически стираемого перепрограммируемого ПЗУ (по технологии EEPROM) размером 2048x38 с контроллером интерфейса AHB со схемой коррекции ошибок (организация памяти 32 плюс 6) и возможностью исполнения программы;

- Возможность подключения внешней памяти по интерфейсу QSPI (до 4МБайт)

- Менеджер загрузки обеспечивает управление выбранным источником загрузки (SPI FLASH, ОЗУ, EEPROM);

Периферийные устройства на шинах

Домен питания

- LDO_BU – регулятор напряжения батарейного домена с низким падением напряжения (входное напряжении 2,5 – 3,6 В, номинальное выходное напряжение 1,8 В, допустимая нагрузка до 5 мА);

- LDO_SYS – основной регулятор напряжения с низким падением напряжения (входное напряжении 3,0 – 3,6 В, номинальное выходное напряжение 1,8 В, допустимая нагрузка до 60 мА);

- WakeUp - обеспечивает управление питанием и сбросом домена 0;

Домен сброса и тактирования

- PORandBor (Power On Reset and BrownOut) – формирователь сигнала сброса батарейного домена при включении питания и контроль снижения напряжения питания ниже заданного;

- блок управления питанием и тактированием обеспечивает управление питанием и управление тактовыми сигналами (установка коэффициентов делителей для шин, отключение тактирования отдельных устройств);

- Внешние генераторы

- OSC32K – генератор с выводами для подключения внешнего часового кварцевого резонатора;

- OSC32M – генератор с выводами для подключения внешнего кварцевого резонатора для тактирования системы с частотой от 1 до 32 МГц;

- Внутренние генераторы

- HSI32M – встроенный генератор с частотой 32 МГц с возможностью корректировки частоты;

- LSI32K встроенных генератора с частотой 32 кГц с возможностью корректировки частоты;

- монитор частоты, предназначен для контроля состояния источников тактирования во время работы микроконтроллера;

Периферийные устройства

- контроллер выводов, обеспечивает управление функциями мультиплексированных выводов, два 16-ти и один 8-ми разрядных порта ввода-вывода общего назначения (GPIO);

- контроллер прерываний обеспечивает поддержку 32 маскируемых прерываний от периферийных устройств;

- CRC32 – модуль, предназначен для вычисления контрольной суммы (CRC) массива данных без использования вычислительных ресурсов центрального процессора на основе произвольного 32х-разрядного полинома;

- ускоритель симметричной криптографии, реализует три специализированных преобразования:

- AES128, FIPS 197 128-битный блочный шифр, со 128-битным ключом;

- «Магма», ГОСТ 34.122015 64х-битный блочный шифр;

- «Кузнечик», ГОСТ 34.122015 128-битный блочный шифр;

- Поддерживает режимы сцепления блоков (ECB, CBC, CTR);часы реального времени с функцией календаря с корректировкой для високосного года и программируемым будильником с возможностью генерации прерываний и регистровым файлом 16х32 бит, для хранения пользовательских данных в батарейном домене;

- три модуля «Таймер32», каждый из которых представляет собой настраиваемый 32х-разрядный счетчик с программируемым делителем и тремя режимами счета (прямой, обратный и двунаправленный). Timer32_1, Timer32_2 дополнительно имеют четыре независимых канала, способных работать в режиме захвата, сравнения или ШИМ;

- контроллер DMA, реализует передачу данных между ведомыми устройствами на коммутационной матрице без участия ядра, имеет четыре независимых канала, обеспечивающих работу в режимах память-память, периферия-периферия, память-периферия с программируемым уровнем приоритетов обработки запросов;

- SPIFI контроллер, обеспечивает интерфейс к внешней флэш-памяти и поддерживает два режима работы: режим работы с периферией и режим работы с памятью. Контроллер обеспечивает выполнение инструкций из внешней памяти и имеет КЭШ-память размером 256х32. Контроллер поддерживает работу в обычном последовательном и в: 2-х и 4-х битном параллельном режимах и обеспечивает возможность исполнения программы;

- цифровая часть аналоговых блоков, обеспечивает доступ со стороны ядра к АЦП, ЦАП, мониторам температуры и напряжения; три «Таймер16», каждый из которых представляет собой настраиваемый 16-ти разрядный счетчик с программируемым делителем (1, 2, 4, 8, 16, 32, 64, 128) с поддержкой режима ШИМ и настраиваемыми входными цифровыми фильтрами;

- два модуля SPI для взаимодействия с различными периферийными устройствами, такими, как микросхемы памяти, датчики температуры, датчики давления, аналоговые преобразователи, часы реального времени, дисплеи и любые SD карты, поддерживающие последовательный режим обмена. Контроллер поддерживает работу в режиме ведущего и ведомого;

- два модуля I2C, обеспечивающих последовательный интерфейс в соответствии со спецификацией на шину I2C от компании Philips/NXP. Контроллер I2C представляет собой двунаправленный, восьмибитный приемо–передатчик для взаимодействия с различными периферийными устройствами;

- два модуля USART - синхронные асинхронные приемник-передатчики, который поддерживают широкий диапазон скоростей передач и форматов данных, задаваемых программно, с возможностью автоматически формировать бит четности и с возможностью обнаружения ошибок;

- 12-ти разрядный АЦП, предназначен для преобразования входного аналогового сигнала в 12-разрядный цифровой код. Количество каналов 8, частота преобразования 1 МГц;

- 12-ти разрядный ЦАП, предназначен для преобразования входного 12- разрядного цифрового кода в аналоговый сигнал. Количество каналов 2, частота преобразования 1 МГц;

- монитор температуры с программируемыми порогами срабатывания;

- два монитора питания напряжением с программируемым порогом срабатывания, котроллируемые напряжения: AVCC и VCC_BAT;

- сторожевой таймер - схема контроля над зависанием системы. Обеспечивает формирование прерывания и сброса, если не был выполнен программный сброс счетчика;