Распиновка и функции выводов: различия между версиями

Нет описания правки |

|||

| (не показаны 42 промежуточные версии этого же участника) | |||

| Строка 1: | Строка 1: | ||

=== Введение === | |||

В микроконтроллер встроены два 16-выводных порта, и один 8-выводный порт. Для каждого порта в карте регистров есть несколько 32-битных регистров настройки: GPIOx_SET_STATUS, GPIOx_RESET, GPIOx_SET_DIRECTION_OUT, GPIOx_SET_DIRECTION_IN, GPIOx_OUTPUT. А так же есть отдельный периферийный блок, который отвечает за дополнительные свойства выводов, включая работу с периферийными блоками: PADx_CFG, PADx_DS, PADx_PUPD. | |||

=== Основные возможности === | |||

* До 16 выводов на каждый порт | |||

* Выходные состояния - выход-мост - 0 или 1, аналоговый выход | |||

* Выходное состояние может приниматься из регистра выхода GPIOx_OUTPUT или из выхода периферийного устройства | |||

* Выбор нагрузочной способности вывода | |||

* Типы входов - плавающее состояние, подтяжка к 1це, подтяжка к 0, аналоговый вход | |||

* Входная информация снимается с регистра GPIOx_SET_STATUS, либо выход может быть направлен на периферийное устройство | |||

* Аналоговая функция | |||

* Альтернативные функции - до 3х дополнительных функции, помимо основной функции программного управления | |||

* Высокоскоростной доступ на шине | |||

* Гибкая система мультиплексирования позволяет переключаться в приложении между несколькими функциями | |||

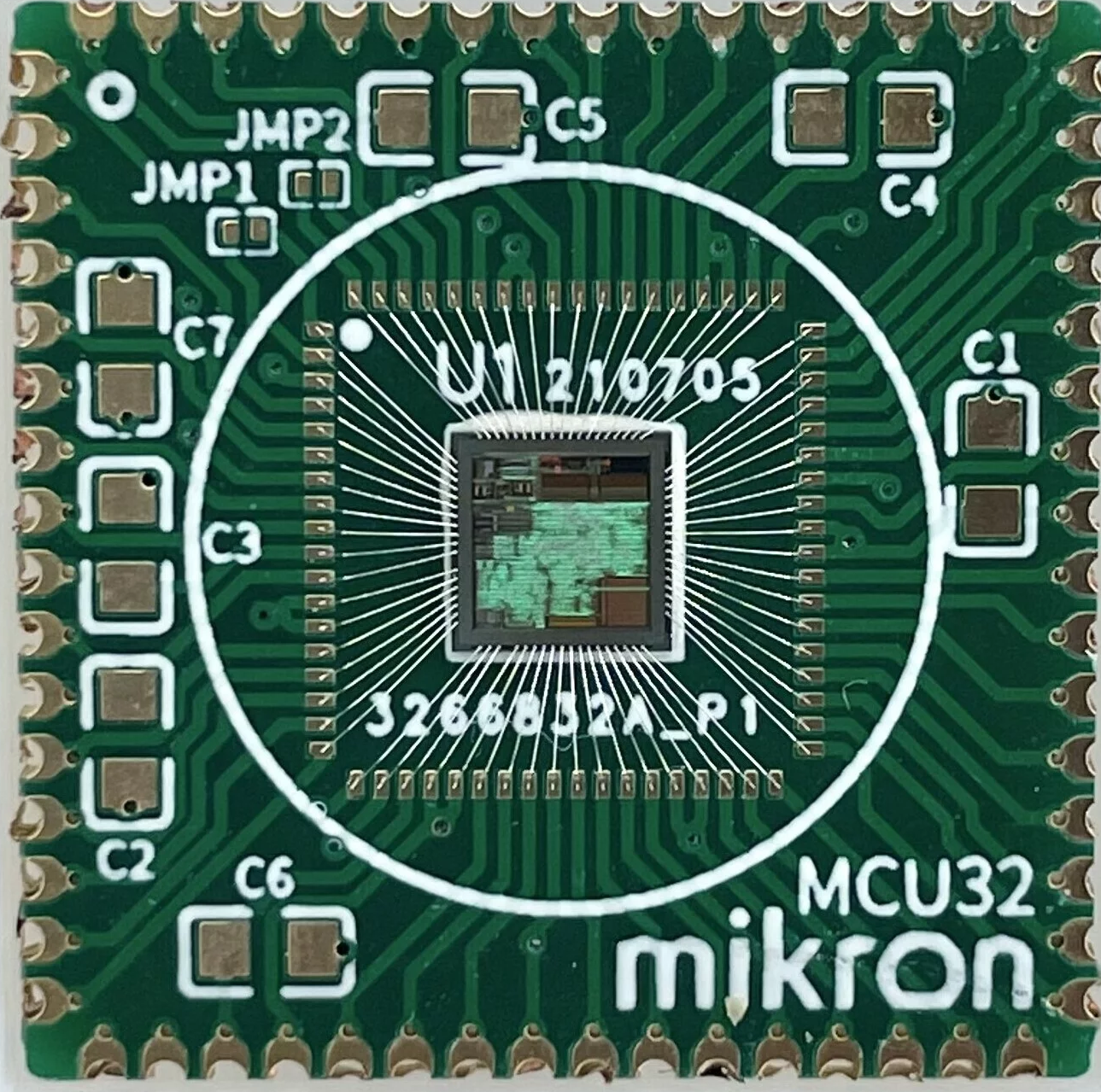

=== Распиновка корпуса === | === Распиновка корпуса === | ||

<<Здесь будет изображение корпуса и наименования | ''Данная распиновка соответствует первой инженерной версии микроконтроллера.'' | ||

Микросхема производится в следующих корпусах: | |||

* QFN-64 (LGA-64) | |||

<<Здесь будет изображение корпуса и наименования выводов>> | |||

Площадка под корпусом не подсоединена. Её можно оставить либо не подключенной, либо подключенной к GND. | |||

=== Таблица выводов === | === Таблица выводов === | ||

{| class="wikitable" | {| class="wikitable" | ||

|+ | |+Таблица выводов | ||

!№ вывода | !№ вывода | ||

!Тип | !Тип | ||

!Наименование | |||

!Главная функция | !Главная функция | ||

!Комментарий | !Комментарий | ||

|- | |- | ||

|1 | |1 | ||

|I/O | |I/O | ||

|PORT_1.12 & DAC1.1 | |PORT_1.12 | ||

|I2C1_sda&DAC1.1 | |||

GPIO_1.12 | |||

UART0_ndtr | UART0_ndtr | ||

|Порт общего назначения | |Порт общего назначения | ||

| Строка 27: | Строка 53: | ||

|PORT_1.11 | |PORT_1.11 | ||

|UART1_rts | |UART1_rts | ||

GPIO_1.11 | |||

REF_DAC | REF_DAC | ||

|Порт общего назначения | |Порт общего назначения | ||

| Строка 37: | Строка 65: | ||

|PORT_1.10 | |PORT_1.10 | ||

|UART1_cts | |UART1_cts | ||

GPIO_1.10 | |||

|Порт общего назначения | |Порт общего назначения | ||

Интерфейс UART_1, готовность передачи | Интерфейс UART_1, готовность передачи | ||

| Строка 44: | Строка 73: | ||

|PORT_1.9 | |PORT_1.9 | ||

|UART1_txd | |UART1_txd | ||

GPIO_1.9 | |||

|Порт общего назначения | |Порт общего назначения | ||

Интерфейс UART_1, данные для передачи | Интерфейс UART_1, данные для передачи | ||

| Строка 55: | Строка 85: | ||

|6 | |6 | ||

|O | |O | ||

| | |Vcap_1 | ||

| | | | ||

|Выход системного LDO для подключения конденсаторов | |Выход системного LDO для подключения конденсаторов | ||

| Строка 62: | Строка 92: | ||

|I/O | |I/O | ||

|PORT_1.8 | |PORT_1.8 | ||

|UART1_rxd | |||

GPIO_1.8 | |||

|Интерфейс UART_1, принимаемые данные | |||

|- | |||

|8 | |||

|PWR | |||

|VBAT | |||

| | |||

|Питание батарейного домена 3,3 В (при отсутствии основного питания на VCC_BU) | |||

|- | |||

| colspan="5" |''Первая ревизия:'' | |||

|- | |||

|''9'' | |||

|''PWR'' | |||

|''VCC_BU'' | |||

| | | | ||

|''Питание батарейного домена 3.3В'' | |||

|- | |||

|''10'' | |||

|''O'' | |||

|''Vcap_bu'' | |||

| | | | ||

|''Выход батарейного LDO для подключения конденсаторов'' | |||

|- | |- | ||

| | |''11'' | ||

|PWR | |''PWR'' | ||

| | |''VSS'' | ||

| | | | ||

| | |''Общий вывод'' | ||

|- | |||

| colspan="5" |Вторая ревизия: | |||

|- | |- | ||

|9 | |9 | ||

| Строка 79: | Строка 132: | ||

|10 | |10 | ||

|PWR | |PWR | ||

| | |VCC_BU | ||

| | | | ||

|Питание батарейного | |Питание батарейного домена 3.3В | ||

|- | |- | ||

|11 | |11 | ||

|O | |O | ||

| | |Vcap_bu | ||

| | | | ||

|Выход батарейного LDO для подключения конденсаторов | |Выход батарейного LDO для подключения конденсаторов | ||

|- | |||

| colspan="5" |<< | |||

|- | |- | ||

|12 | |12 | ||

| Строка 147: | Строка 202: | ||

|PORT_1.7 | |PORT_1.7 | ||

|SPI1_n_ss_out_3 | |SPI1_n_ss_out_3 | ||

GPIO_1.7 | |||

digital_test_pad | digital_test_pad | ||

| Строка 161: | Строка 218: | ||

|PORT_1.6 | |PORT_1.6 | ||

|SPI1_n_ss_out_2 | |SPI1_n_ss_out_2 | ||

GPIO_1.6 | |||

UART0_ddis | UART0_ddis | ||

|Порт общего назначения | |Порт общего назначения | ||

| Строка 171: | Строка 230: | ||

|PORT_1.5 | |PORT_1.5 | ||

|SPI1_n_ss_out_1 | |SPI1_n_ss_out_1 | ||

GPIO_1.5 | |||

UART0_ck | UART0_ck | ||

ADC1.0 | ADC1.0 | ||

|Порт общего назначения | |Порт общего назначения | ||

| Строка 181: | Строка 243: | ||

|- | |- | ||

|24 | |24 | ||

| | |O | ||

| | |Vcap_2 | ||

| | | | ||

|Выход системного LDO для подключения конденсаторов | |Выход системного LDO для подключения конденсаторов | ||

| Строка 190: | Строка 252: | ||

|PORT_1.4 | |PORT_1.4 | ||

|SPI1_n_ss_out_0 | |SPI1_n_ss_out_0 | ||

GPIO_1.4 | |||

Timer32_2_Tx | Timer32_2_Tx | ||

|Порт общего назначения | |Порт общего назначения | ||

| Строка 200: | Строка 264: | ||

|PORT_1.3 | |PORT_1.3 | ||

|SPI1_n_ss_in | |SPI1_n_ss_in | ||

GPIO_1.3 | |||

Timer32_2_ch4 | Timer32_2_ch4 | ||

|Порт общего назначения | |Порт общего назначения | ||

| Строка 210: | Строка 276: | ||

|PORT_1.2 | |PORT_1.2 | ||

|SPI1_clk | |SPI1_clk | ||

GPIO_1.2 | |||

Timer32_2_ch3 | Timer32_2_ch3 | ||

|Порт общего назначения | |Порт общего назначения | ||

| Строка 220: | Строка 288: | ||

|PORT_1.1 | |PORT_1.1 | ||

|SPI1_mosi | |SPI1_mosi | ||

GPIO_1.1 | |||

Timer32_2_ch2 | Timer32_2_ch2 | ||

|Порт общего назначения | |Порт общего назначения | ||

| Строка 236: | Строка 306: | ||

|PORT_1.0 | |PORT_1.0 | ||

|SPI1_miso | |SPI1_miso | ||

GPIO_1.0 | |||

Timer32_2_ch1 | Timer32_2_ch1 | ||

|Порт общего назначения | |Порт общего назначения | ||

| Строка 246: | Строка 318: | ||

|PORT_2.7 | |PORT_2.7 | ||

|UART1_ddis | |UART1_ddis | ||

GPIO_2.7 | |||

|Порт общего назначения | |Порт общего назначения | ||

Интерфейс UART_1, Сигнал считывания принятых данных | Интерфейс UART_1, Сигнал считывания принятых данных | ||

| Строка 253: | Строка 326: | ||

|PORT_2.6 | |PORT_2.6 | ||

|SPI0_n_ss_out_3 | |SPI0_n_ss_out_3 | ||

GPIO_2.6 | |||

UART1_ck | UART1_ck | ||

|Порт общего назначения | |Порт общего назначения | ||

Интерфейс SPI_0, сигнал выбора ведомого 3 | Интерфейс SPI_0, сигнал выбора ведомого 3 | ||

Интерфейс UART_1 | Интерфейс UART_1 | ||

Сигнал синхронизации для приема и передачи | |||

|- | |- | ||

|33 | |33 | ||

| Строка 262: | Строка 339: | ||

|PORT_2.5 | |PORT_2.5 | ||

|SPIFI_DATA_3 | |SPIFI_DATA_3 | ||

GPIO_2.5 | |||

|Порт общего назначения | |Порт общего назначения | ||

Интерфейс SPIFI, шина данных, разряд 3 | Интерфейс SPIFI, шина данных, разряд 3 | ||

| Строка 269: | Строка 347: | ||

|PORT_2.4 | |PORT_2.4 | ||

|SPIFI_DATA_2 | |SPIFI_DATA_2 | ||

GPIO_2.4 | |||

|Порт общего назначения | |Порт общего назначения | ||

Интерфейс SPIFI, шина данных, разряд 2 | Интерфейс SPIFI, шина данных, разряд 2 | ||

| Строка 276: | Строка 355: | ||

|PORT_2.3 | |PORT_2.3 | ||

|SPIFI_DATA_1 | |SPIFI_DATA_1 | ||

GPIO_2.3 | |||

UART1_ri | |||

|Порт общего назначения | |Порт общего назначения | ||

Интерфейс SPIFI, шина данных, разряд 1 | Интерфейс SPIFI, шина данных, разряд 1 | ||

Интерфейс UART_1, Звонок (вызов) на телефонной линии | |||

|- | |- | ||

|36 | |36 | ||

| Строка 283: | Строка 367: | ||

|PORT_2.2 | |PORT_2.2 | ||

|SPIFI_DATA_0 | |SPIFI_DATA_0 | ||

GPIO_2.2 | |||

UART1_dsr | |||

|Порт общего назначения | |Порт общего назначения | ||

Интерфейс SPIFI, шина данных, разряд 0 | Интерфейс SPIFI, шина данных, разряд 0 | ||

Интерфейс UART_1, Сигнал готовности источника данных | |||

|- | |- | ||

|37 | |37 | ||

| Строка 290: | Строка 379: | ||

|PORT_2.1 | |PORT_2.1 | ||

|SPIFI_CS | |SPIFI_CS | ||

GPIO_2.1 | |||

UART1_dcd | UART1_dcd | ||

|Порт общего назначения | |Порт общего назначения | ||

| Строка 299: | Строка 390: | ||

|PORT_2.0 | |PORT_2.0 | ||

|SPIFI_SCLK | |SPIFI_SCLK | ||

GPIO_2.0 | |||

UART1_dtr | UART1_dtr | ||

|Порт общего назначения | |Порт общего назначения | ||

| Строка 318: | Строка 411: | ||

|41 | |41 | ||

|O | |O | ||

| | |Vcap_3 | ||

| | | | ||

|Выход системного LDO для подключения конденсаторов | |Выход системного LDO для подключения конденсаторов | ||

|- | |- | ||

|42 | |42 | ||

| | |I/O | ||

| | |PORT_0.15 | ||

| | |TDO | ||

| | GPIO_0.15 | ||

|Порт общего назначения | |||

Интерфейс JTAG. Выход данных | |||

|- | |- | ||

|43 | |43 | ||

| | |I/O | ||

| | |PORT_0.14 | ||

| | |TRSTn | ||

| | GPIO_0.14 | ||

|Порт общего назначения | |||

Интерфейс JTAG. Сброс (активный уровень 0) | |||

|- | |- | ||

|44 | |44 | ||

| | |I/O | ||

| | |PORT_0.13 | ||

| | |TMS | ||

| | GPIO_0.13 | ||

Timer16_2_out | |||

ADC1.7 | |||

|Порт общего назначения | |||

Интерфейс JTAG. Сигнала управление | |||

16-разрядный таймер 2. Выход | |||

Канал АЦП | |||

|- | |- | ||

|45 | |45 | ||

| | |I/O | ||

| | |PORT_0.12 | ||

| | |TCK | ||

| | GPIO_0.12 | ||

Timer16_2_in2 | |||

|Порт общего назначения | |||

Интерфейс JTAG. Сигнал тактирования | |||

16-разрядный таймер 2. Вход 2 | |||

|- | |- | ||

|46 | |46 | ||

| | |I/O | ||

| | |PORT_0.11 | ||

| | |TDI | ||

| | GPIO_0.11 | ||

Timer16_2_in1 | |||

ADC1.6 | |||

|Порт общего назначения | |||

Интерфейс JTAG. Вход данных | |||

16-разрядный таймер 2. Вход 1 | |||

Канал АЦП | |||

|- | |- | ||

|47 | |47 | ||

| | |I/O | ||

| | |PORT_0.10 | ||

| | |I<sup>2</sup>C0_scl | ||

| | GPIO_0.10 | ||

Timer16_1_out | |||

|Порт общего назначения | |||

Интерфейс I<sup>2</sup>C_0, сигнал тактирования | |||

16-разрядный таймер 1. Выход | |||

|- | |- | ||

|48 | |48 | ||

| | |I/O | ||

| | |PORT_0.9 | ||

| | |I<sup>2</sup>C0_sda | ||

| | GPIO_0.9 | ||

Timer16_1_in2 | |||

ADC1.5 | |||

|Порт общего назначения | |||

Интерфейс I<sup>2</sup>C_0, линия данных | |||

16-разрядный таймер 1. Вход 2 | |||

Канал АЦП | |||

|- | |- | ||

|49 | |49 | ||

| | |I/O | ||

| | |PORT_0.8 | ||

| | |UART0_rts | ||

| | GPIO_0.8 | ||

Timer16_1_in1 | |||

|Порт общего назначения | |||

Интерфейс UART_0, запрос на передачу | |||

16-разрядный таймер 1. Вход 1 | |||

|- | |- | ||

|50 | |50 | ||

| | |I/O | ||

| | |PORT_0.7 | ||

| | |UART0_cts | ||

| | GPIO_0.7 | ||

Timer16_0_out | |||

ADC1.4 | |||

|Порт общего назначения | |||

Интерфейс UART_0, готовность передачи | |||

16-разрядный таймер 0. Выход | |||

Канал АЦП | |||

|- | |- | ||

|51 | |51 | ||

| | |I/O | ||

| | |PORT_0.6 | ||

| | |UART0_txd | ||

| | GPIO_0.6 | ||

Timer16_0_in2 | |||

|Порт общего назначения | |||

Интерфейс UART_0, данные для передачи | |||

16-разрядный таймер 0. Вход 2 | |||

|- | |- | ||

|52 | |52 | ||

|PWR | |||

|VCC | |||

| | | | ||

| | |Основное питание 3,3 В | ||

|- | |- | ||

|53 | |53 | ||

| | |I/O | ||

| | |PORT_0.5 | ||

| | |UART0_rxd | ||

| | GPIO_0.5 | ||

Timer16_0_in1 | |||

|Порт общего назначения | |||

Интерфейс UART_0, принимаемые данные | |||

16-разрядный таймер 0. Вход 1 | |||

|- | |- | ||

|54 | |54 | ||

| | |I/O | ||

| | |PORT_0.4 | ||

| | |SPI0_n_ss_out_0 | ||

| | GPIO_0.4 | ||

Timer32_1_Tx | |||

ADC1.3 | |||

|Порт общего назначения | |||

Интерфейс SPI_0, сигнал выбора ведомого 0 | |||

32х-разрядный таймер 1. Внешний вход тактирования | |||

Канал АЦП | |||

|- | |- | ||

|55 | |55 | ||

| | |I/O | ||

| | |PORT_0.3 | ||

| | |SPI0_n_ss_in | ||

| | GPIO_0.3 | ||

Timer32_1_ch4 | |||

|Порт общего назначения | |||

Интерфейс SPI_0, сигнал выбора в режиме ведомого | |||

32х-разрядный таймер1. Канал 4 (ШИМ, захват, сравнение) | |||

|- | |- | ||

|56 | |56 | ||

| | |I/O | ||

| | |PORT_0.2 | ||

| | |SPI0_clk | ||

| | GPIO_0.2 | ||

Timer32_1_ch3 | |||

ADC1.2 | |||

|Порт общего назначения | |||

Интерфейс SPI_0, тактовый сигнал | |||

32х-разрядный таймер1. Канал 3 (ШИМ, захват, сравнение) | |||

Канал АЦП | |||

|- | |- | ||

|57 | |57 | ||

| | |I/O | ||

| | |PORT_0.1 | ||

| | |SPI0_mosi | ||

| | GPIO_0.1 | ||

Timer32_1_ch2 | |||

|Порт общего назначения | |||

Интерфейс SPI_0, линия данных от ведущего к ведомому | |||

32х-разрядный таймер1. Канал 2 (ШИМ, захват, сравнение) | |||

|- | |- | ||

|58 | |58 | ||

| | |I/O | ||

| | |PORT_0.0 | ||

| | |SPI0_miso | ||

| | GPIO_0.0 | ||

Timer32_1_ch1 | |||

REF_TST | |||

|Порт общего назначения | |||

Интерфейс SPI_0, линия данных от ведомого к ведущему | |||

32х-разрядный таймер1. Канал 1 (ШИМ, захват, сравнение) | |||

Внешний опорный сигнал для тестирования | |||

|- | |- | ||

|59 | |59 | ||

|PWR | |||

|VSS | |||

| | | | ||

| | |Общий вывод | ||

|- | |- | ||

|60 | |60 | ||

| | |I/O | ||

| | |PORT_1.15 | ||

| | |SPI0_n_ss_out_2 | ||

| | GPIO_1.15 | ||

UART0_nri | |||

TEST OUT | |||

|Порт общего назначения | |||

Интерфейс SPI_0, сигнал выбора ведомого 2 | |||

Интерфейс UART_0 Звонок (вызов) на телефонной линии | |||

Выход системы аналогового тестирования | |||

|- | |- | ||

|61 | |61 | ||

| | |I/O | ||

| | |PORT_1.14 | ||

| | |SPI0_n_ss_out_1 | ||

| | GPIO_1.14 | ||

UART0_ndsr | |||

|Порт общего назначения | |||

Интерфейс SPI_0, сигнал выбора ведомого 1 | |||

Интерфейс UART_0, Сигнал готовности источника данных | |||

|- | |- | ||

|62 | |62 | ||

|PWR | |||

|AVCC | |||

| | | | ||

| | |Питание аналоговых блоков 3,3 В | ||

|- | |- | ||

|63 | |63 | ||

|PWR | |||

|AGND | |||

| | | | ||

| | |Общий вывод аналоговых блоков | ||

|- | |- | ||

|64 | |64 | ||

| | |I/O | ||

| | |PORT_1.13 | ||

| | |DAC_2 &I<sup>2</sup>C1_scl | ||

| | GPIO_1.13 | ||

UART0_ndcd | |||

|Канал ЦАП | |||

Порт общего назначения | |||

Интерфейс I<sup>2</sup>C 1, сигнал тактирования | |||

Интерфейс UART_0, Сигнал обнаружения не-сущей | |||

|} | |} | ||

=== | === Функции выводов ревизии 0 === | ||

{| class="wikitable" | {| class="wikitable" | ||

|+ | |+Функции выводов, под ревизию 0 | ||

! colspan="2" rowspan="2" |Порт | ! colspan="2" rowspan="2" |Порт | ||

! colspan="4" |Pad_control | ! colspan="4" |Pad_control | ||

| Строка 649: | Строка 881: | ||

|- | |- | ||

|1.13 | |1.13 | ||

| | |DAC_2&I<sup>2</sup>C1_scl | ||

|GPIO_1.13 | |GPIO_1.13 | ||

| | | | ||

| | | - | ||

|- | |- | ||

|1.14 | |1.14 | ||

| | |SPI0_n_ss_out_1 | ||

|GPIO_1.14 | |GPIO_1.14 | ||

| | | | ||

| | | - | ||

|- | |- | ||

|1.15 | |1.15 | ||

| | |SPI0_n_ss_out_2 | ||

|GPIO_1.15 | |GPIO_1.15 | ||

| | | | ||

| | |TEST OUT | ||

|- | |- | ||

| rowspan="8" |Порт 2 | | rowspan="8" |Порт 2 | ||

| Строка 715: | Строка 947: | ||

| - | | - | ||

|} | |} | ||

=== Функции выводов ревизии 2 === | |||

{| class="wikitable" | |||

|+Функции выводов, под ревизию 2 | |||

! colspan="2" rowspan="2" |Порт | |||

! colspan="4" |Pad_control | |||

|- | |||

!00 | |||

!01 | |||

!02 | |||

!03 | |||

|- | |||

| rowspan="16" |Порт 0 | |||

|0.0 | |||

|GPIO_0.0 | |||

|SPI0_miso | |||

|Timer32_1_ch1 | |||

|REF_TST | |||

|- | |||

|0.1 | |||

|GPIO_0.1 | |||

|SPI0_mosi | |||

|Timer32_1_ch2 | |||

| - | |||

|- | |||

|0.2 | |||

|GPIO_0.2 | |||

|SPI0_clk | |||

|Timer32_1_ch3 | |||

|ADC1.2 | |||

|- | |||

|0.3 | |||

|GPIO_0.3 | |||

|SPI0_n_ss_in | |||

|Timer32_1_ch4 | |||

| - | |||

|- | |||

|0.4 | |||

|GPIO_0.4 | |||

|SPI0_n_ss_out_0 | |||

|Timer32_1_Tx | |||

|ADC1.3 | |||

|- | |||

|0.5 | |||

|GPIO_0.5 | |||

|UART0_rxd | |||

|Timer16_0_in1 | |||

| - | |||

|- | |||

|0.6 | |||

|GPIO_0.6 | |||

|UART0_txd | |||

|Timer16_0_in2 | |||

| - | |||

|- | |||

|0.7 | |||

|GPIO_0.7 | |||

|UART0_cts | |||

|Timer16_0_out | |||

|ADC1.4 | |||

|- | |||

|0.8 | |||

|GPIO_0.8 | |||

|UART0_rts | |||

|Timer16_1_in1 | |||

| - | |||

|- | |||

|0.9 | |||

|GPIO_0.9 | |||

|I<sup>2</sup>C0_sda | |||

|Timer16_1_in2 | |||

|ADC1.5 | |||

|- | |||

|0.10 | |||

|GPIO_0.10 | |||

|I<sup>2</sup>C0_scl | |||

|Timer16_1_out | |||

| - | |||

|- | |||

|0.11 | |||

|GPIO_0.11 | |||

|TDI | |||

|Timer16_2_in1 | |||

|ADC1.6 | |||

|- | |||

|0.12 | |||

|GPIO_0.12 | |||

|TCK | |||

|Timer16_2_in2 | |||

| - | |||

|- | |||

|0.13 | |||

|GPIO_0.13 | |||

|TMS | |||

|Timer16_2_out | |||

|ADC1.7 | |||

|- | |||

|0.14 | |||

|GPIO_0.14 | |||

|TRSTn | |||

| - | |||

| - | |||

|- | |||

|0.15 | |||

|GPIO_0.15 | |||

|TDO | |||

| - | |||

| - | |||

|- | |||

| rowspan="16" |Порт 1 | |||

|1.0 | |||

|GPIO_1.0 | |||

|SPI1_miso | |||

|Timer32_2_ch1 | |||

| - | |||

|- | |||

|1.1 | |||

|GPIO_1.1 | |||

|SPI1_mosi | |||

|Timer32_2_ch2 | |||

| - | |||

|- | |||

|1.2 | |||

|GPIO_1.2 | |||

|SPI1_clk | |||

|Timer32_2_ch3 | |||

| - | |||

|- | |||

|1.3 | |||

|GPIO_1.3 | |||

|SPI1_n_ss_in | |||

|Timer32_2_ch4 | |||

| - | |||

|- | |||

|1.4 | |||

|GPIO_1.4 | |||

|SPI1_n_ss_out_0 | |||

|Timer32_2_Tx | |||

| - | |||

|- | |||

|1.5 | |||

|GPIO_1.5 | |||

|SPI1_n_ss_out_1 | |||

|UART0_ck | |||

|ADC1.0 | |||

|- | |||

|1.6 | |||

|GPIO_1.6 | |||

|SPI1_n_ss_out_2 | |||

|UART0_ddis | |||

| - | |||

|- | |||

|1.7 | |||

|GPIO_1.7 | |||

|SPI1_n_ss_out_3 | |||

|digital_test_pad | |||

|ADC1.1 | |||

|- | |||

|1.8 | |||

|GPIO_1.8 | |||

|UART1_rxd | |||

| - | |||

| - | |||

|- | |||

|1.9 | |||

|GPIO_1.9 | |||

|UART1_txd | |||

| - | |||

| - | |||

|- | |||

|1.10 | |||

|GPIO_1.10 | |||

|UART1_cts | |||

| - | |||

|REF_ADC | |||

|- | |||

|1.11 | |||

|GPIO_1.11 | |||

|UART1_rts | |||

| - | |||

|REF_DAC | |||

|- | |||

|1.12 | |||

|GPIO_1.12 | |||

|I<sup>2</sup>C1_sda | |||

|UART0_ndtr | |||

| - | |||

|- | |||

|1.13 | |||

|GPIO_1.13 | |||

|DAC_2&I<sup>2</sup>C1_scl | |||

| | |||

| - | |||

|- | |||

|1.14 | |||

|GPIO_1.14 | |||

|SPI0_n_ss_out_1 | |||

| | |||

| - | |||

|- | |||

|1.15 | |||

|GPIO_1.15 | |||

|SPI0_n_ss_out_2 | |||

| | |||

|TEST OUT | |||

|- | |||

| rowspan="8" |Порт 2 | |||

|2.0 | |||

|GPIO_2.0 | |||

|SPIFI_SCLK | |||

|UART1_dtr | |||

| - | |||

|- | |||

|2.1 | |||

|GPIO_2.1 | |||

|SPIFI_CS | |||

|UART1_dcd | |||

| - | |||

|- | |||

|2.2 | |||

|GPIO_2.2 | |||

|SPIFI_DATA_0 | |||

|UART1_dsr | |||

| - | |||

|- | |||

|2.3 | |||

|GPIO_2.3 | |||

|SPIFI_DATA_1 | |||

|UART1_ri | |||

| - | |||

|- | |||

|2.4 | |||

|GPIO_2.4 | |||

|SPIFI_DATA_2 | |||

| - | |||

| - | |||

|- | |||

|2.5 | |||

|GPIO_2.5 | |||

|SPIFI_DATA_3 | |||

| - | |||

| - | |||

|- | |||

|2.6 | |||

|GPIO_2.6 | |||

|SPI0_n_ss_out_3 | |||

|UART1_ck | |||

| - | |||

|- | |||

|2.7 | |||

|GPIO_2.7 | |||

| - | |||

|UART1_ddis | |||

| - | |||

|} | |||

Выводы, относящиеся к JTAG P0.11-P0.15 по-умолчанию сконфигурированы в режим 1. Остальные выводы - в режиме 0. | |||

При запуске микроконтроллера в режиме SPIFI выводы P2.0-P2.5 при по-умолчанию автоматически инициализируются в режим 1, в иных вариантах загрузки выводы остаются в режиме 0. | |||

Текущая версия от 09:00, 21 октября 2023

Введение

В микроконтроллер встроены два 16-выводных порта, и один 8-выводный порт. Для каждого порта в карте регистров есть несколько 32-битных регистров настройки: GPIOx_SET_STATUS, GPIOx_RESET, GPIOx_SET_DIRECTION_OUT, GPIOx_SET_DIRECTION_IN, GPIOx_OUTPUT. А так же есть отдельный периферийный блок, который отвечает за дополнительные свойства выводов, включая работу с периферийными блоками: PADx_CFG, PADx_DS, PADx_PUPD.

Основные возможности

- До 16 выводов на каждый порт

- Выходные состояния - выход-мост - 0 или 1, аналоговый выход

- Выходное состояние может приниматься из регистра выхода GPIOx_OUTPUT или из выхода периферийного устройства

- Выбор нагрузочной способности вывода

- Типы входов - плавающее состояние, подтяжка к 1це, подтяжка к 0, аналоговый вход

- Входная информация снимается с регистра GPIOx_SET_STATUS, либо выход может быть направлен на периферийное устройство

- Аналоговая функция

- Альтернативные функции - до 3х дополнительных функции, помимо основной функции программного управления

- Высокоскоростной доступ на шине

- Гибкая система мультиплексирования позволяет переключаться в приложении между несколькими функциями

Распиновка корпуса

Данная распиновка соответствует первой инженерной версии микроконтроллера.

Микросхема производится в следующих корпусах:

- QFN-64 (LGA-64)

<<Здесь будет изображение корпуса и наименования выводов>>

Площадка под корпусом не подсоединена. Её можно оставить либо не подключенной, либо подключенной к GND.

Таблица выводов

| № вывода | Тип | Наименование | Главная функция | Комментарий |

|---|---|---|---|---|

| 1 | I/O | PORT_1.12 | I2C1_sda&DAC1.1

GPIO_1.12 UART0_ndtr |

Порт общего назначения

ЦАП Интерфейс I2C_1, линия данных Интерфейс UART_0 Готовность данных приемника |

| 2 | I/O | PORT_1.11 | UART1_rts

GPIO_1.11 REF_DAC |

Порт общего назначения

Интерфейс UART_1, запрос на передачу REF_DAC Внешний опорный сиг-нал ЦАП |

| 3 | I/O | PORT_1.10 | UART1_cts

GPIO_1.10 |

Порт общего назначения

Интерфейс UART_1, готовность передачи |

| 4 | I/O | PORT_1.9 | UART1_txd

GPIO_1.9 |

Порт общего назначения

Интерфейс UART_1, данные для передачи |

| 5 | PWR | VCC | Основное питание 3,3 В | |

| 6 | O | Vcap_1 | Выход системного LDO для подключения конденсаторов | |

| 7 | I/O | PORT_1.8 | UART1_rxd

GPIO_1.8 |

Интерфейс UART_1, принимаемые данные |

| 8 | PWR | VBAT | Питание батарейного домена 3,3 В (при отсутствии основного питания на VCC_BU) | |

| Первая ревизия: | ||||

| 9 | PWR | VCC_BU | Питание батарейного домена 3.3В | |

| 10 | O | Vcap_bu | Выход батарейного LDO для подключения конденсаторов | |

| 11 | PWR | VSS | Общий вывод | |

| Вторая ревизия: | ||||

| 9 | PWR | VSS | Общий вывод | |

| 10 | PWR | VCC_BU | Питание батарейного домена 3.3В | |

| 11 | O | Vcap_bu | Выход батарейного LDO для подключения конденсаторов | |

| << | ||||

| 12 | O | OSC32k_XO | Выход осциллятора 32К | |

| 13 | I | OSC32k_XI | Вход осциллятора 32К | |

| 14 | I | RST | Внешний сброс (активный уровень «0») | |

| 15 | I | EXT_WU | Выход из режима пониженного потребления | |

| 16 | O | RTC_ALARM | Будильник (активный уровень «1») | |

| 17 | I | BOOT_0 | Выбора устройтвом загрузки (бит 0) | |

| 18 | I | BOOT_1 | Выбора устройтвом загрузки (бит 1) | |

| 19 | PWR | VPRG | Напряжение программирования OTP 8,0 В | |

| 20 | PWR | VCC | Основное питание 3,3 В | |

| 21 | I/O | PORT_1.7 | SPI1_n_ss_out_3

GPIO_1.7 digital_test_pad ADC1.1 |

Порт общего назначения

Интерфейс SPI_1, сигнал выбора ведомого 3 Выход цифровой подсистемы тестирования аналоговых блоков Канал АЦП |

| 22 | I/O | PORT_1.6 | SPI1_n_ss_out_2

GPIO_1.6 UART0_ddis |

Порт общего назначения

Интерфейс SPI_1, сигнал выбора ведо-мого 2 Интерфейс UART_0, Сигнал считывания принятых данных |

| 23 | I/O | PORT_1.5 | SPI1_n_ss_out_1

GPIO_1.5 UART0_ck ADC1.0 |

Порт общего назначения

Интерфейс SPI_1, сигнал выбора ведомого 1 Интерфейс UART_0, Сигнал синхронизации для приема и передачи Канал АЦП |

| 24 | O | Vcap_2 | Выход системного LDO для подключения конденсаторов | |

| 25 | I/O | PORT_1.4 | SPI1_n_ss_out_0

GPIO_1.4 Timer32_2_Tx |

Порт общего назначения

Интерфейс SPI_0, сигнал выбора ведомого 0 32х-разрядный таймер2. Внешний вход тактирования |

| 26 | I/O | PORT_1.3 | SPI1_n_ss_in

GPIO_1.3 Timer32_2_ch4 |

Порт общего назначения

Интерфейс SPI_1, сигнал выбора в режиме ведомого 32х-разрядный таймер2. Канал 4 (ШИМ, захват, сравнение) |

| 27 | I/O | PORT_1.2 | SPI1_clk

GPIO_1.2 Timer32_2_ch3 |

Порт общего назначения

Интерфейс SPI_0, тактовый сигнал 32х-разрядный таймер2. Канал 3 (ШИМ, захват, сравнение) |

| 28 | I/O | PORT_1.1 | SPI1_mosi

GPIO_1.1 Timer32_2_ch2 |

Порт общего назначения

Интерфейс SPI_1, линия данных от ведущего к ведомому 32х-разрядный таймер2. Канал 2 (ШИМ, захват, сравнение) |

| 29 | PWR | VSS | Общий вывод | |

| 30 | I/O | PORT_1.0 | SPI1_miso

GPIO_1.0 Timer32_2_ch1 |

Порт общего назначения

Интерфейс SPI_1, линия данных от ведомого к ведущему 32х-разрядный таймер2. Канал 1 (ШИМ, захват, сравнение) |

| 31 | I/O | PORT_2.7 | UART1_ddis

GPIO_2.7 |

Порт общего назначения

Интерфейс UART_1, Сигнал считывания принятых данных |

| 32 | I/O | PORT_2.6 | SPI0_n_ss_out_3

GPIO_2.6 UART1_ck |

Порт общего назначения

Интерфейс SPI_0, сигнал выбора ведомого 3 Интерфейс UART_1 Сигнал синхронизации для приема и передачи |

| 33 | I/O | PORT_2.5 | SPIFI_DATA_3

GPIO_2.5 |

Порт общего назначения

Интерфейс SPIFI, шина данных, разряд 3 |

| 34 | I/O | PORT_2.4 | SPIFI_DATA_2

GPIO_2.4 |

Порт общего назначения

Интерфейс SPIFI, шина данных, разряд 2 |

| 35 | I/O | PORT_2.3 | SPIFI_DATA_1

GPIO_2.3 UART1_ri |

Порт общего назначения

Интерфейс SPIFI, шина данных, разряд 1 Интерфейс UART_1, Звонок (вызов) на телефонной линии |

| 36 | I/O | PORT_2.2 | SPIFI_DATA_0

GPIO_2.2 UART1_dsr |

Порт общего назначения

Интерфейс SPIFI, шина данных, разряд 0 Интерфейс UART_1, Сигнал готовности источника данных |

| 37 | I/O | PORT_2.1 | SPIFI_CS

GPIO_2.1 UART1_dcd |

Порт общего назначения

Интерфейс SPIFI, сигнал CS Интерфейс UART_1, Сигнал обнаружения несущей |

| 38 | I/O | PORT_2.0 | SPIFI_SCLK

GPIO_2.0 UART1_dtr |

Порт общего назначения

Интерфейс SPIFI, тактовый сигнал Интерфейс UART_1, Готовность приемника данных |

| 39 | OSC_O | OSC32M_XO | Выход осциллятора 32М | |

| 40 | OSC_I | OSC32M_XI | Вход осциллятора 32М | |

| 41 | O | Vcap_3 | Выход системного LDO для подключения конденсаторов | |

| 42 | I/O | PORT_0.15 | TDO

GPIO_0.15 |

Порт общего назначения

Интерфейс JTAG. Выход данных |

| 43 | I/O | PORT_0.14 | TRSTn

GPIO_0.14 |

Порт общего назначения

Интерфейс JTAG. Сброс (активный уровень 0) |

| 44 | I/O | PORT_0.13 | TMS

GPIO_0.13 Timer16_2_out ADC1.7 |

Порт общего назначения

Интерфейс JTAG. Сигнала управление 16-разрядный таймер 2. Выход Канал АЦП |

| 45 | I/O | PORT_0.12 | TCK

GPIO_0.12 Timer16_2_in2 |

Порт общего назначения

Интерфейс JTAG. Сигнал тактирования 16-разрядный таймер 2. Вход 2 |

| 46 | I/O | PORT_0.11 | TDI

GPIO_0.11 Timer16_2_in1 ADC1.6 |

Порт общего назначения

Интерфейс JTAG. Вход данных 16-разрядный таймер 2. Вход 1 Канал АЦП |

| 47 | I/O | PORT_0.10 | I2C0_scl

GPIO_0.10 Timer16_1_out |

Порт общего назначения

Интерфейс I2C_0, сигнал тактирования 16-разрядный таймер 1. Выход |

| 48 | I/O | PORT_0.9 | I2C0_sda

GPIO_0.9 Timer16_1_in2 ADC1.5 |

Порт общего назначения

Интерфейс I2C_0, линия данных 16-разрядный таймер 1. Вход 2 Канал АЦП |

| 49 | I/O | PORT_0.8 | UART0_rts

GPIO_0.8 Timer16_1_in1 |

Порт общего назначения

Интерфейс UART_0, запрос на передачу 16-разрядный таймер 1. Вход 1 |

| 50 | I/O | PORT_0.7 | UART0_cts

GPIO_0.7 Timer16_0_out ADC1.4 |

Порт общего назначения

Интерфейс UART_0, готовность передачи 16-разрядный таймер 0. Выход Канал АЦП |

| 51 | I/O | PORT_0.6 | UART0_txd

GPIO_0.6 Timer16_0_in2 |

Порт общего назначения

Интерфейс UART_0, данные для передачи 16-разрядный таймер 0. Вход 2 |

| 52 | PWR | VCC | Основное питание 3,3 В | |

| 53 | I/O | PORT_0.5 | UART0_rxd

GPIO_0.5 Timer16_0_in1 |

Порт общего назначения

Интерфейс UART_0, принимаемые данные 16-разрядный таймер 0. Вход 1 |

| 54 | I/O | PORT_0.4 | SPI0_n_ss_out_0

GPIO_0.4 Timer32_1_Tx ADC1.3 |

Порт общего назначения

Интерфейс SPI_0, сигнал выбора ведомого 0 32х-разрядный таймер 1. Внешний вход тактирования Канал АЦП |

| 55 | I/O | PORT_0.3 | SPI0_n_ss_in

GPIO_0.3 Timer32_1_ch4 |

Порт общего назначения

Интерфейс SPI_0, сигнал выбора в режиме ведомого 32х-разрядный таймер1. Канал 4 (ШИМ, захват, сравнение) |

| 56 | I/O | PORT_0.2 | SPI0_clk

GPIO_0.2 Timer32_1_ch3 ADC1.2 |

Порт общего назначения

Интерфейс SPI_0, тактовый сигнал 32х-разрядный таймер1. Канал 3 (ШИМ, захват, сравнение) Канал АЦП |

| 57 | I/O | PORT_0.1 | SPI0_mosi

GPIO_0.1 Timer32_1_ch2 |

Порт общего назначения

Интерфейс SPI_0, линия данных от ведущего к ведомому 32х-разрядный таймер1. Канал 2 (ШИМ, захват, сравнение) |

| 58 | I/O | PORT_0.0 | SPI0_miso

GPIO_0.0 Timer32_1_ch1 REF_TST |

Порт общего назначения

Интерфейс SPI_0, линия данных от ведомого к ведущему 32х-разрядный таймер1. Канал 1 (ШИМ, захват, сравнение) Внешний опорный сигнал для тестирования |

| 59 | PWR | VSS | Общий вывод | |

| 60 | I/O | PORT_1.15 | SPI0_n_ss_out_2

GPIO_1.15 UART0_nri TEST OUT |

Порт общего назначения

Интерфейс SPI_0, сигнал выбора ведомого 2 Интерфейс UART_0 Звонок (вызов) на телефонной линии Выход системы аналогового тестирования |

| 61 | I/O | PORT_1.14 | SPI0_n_ss_out_1

GPIO_1.14 UART0_ndsr |

Порт общего назначения

Интерфейс SPI_0, сигнал выбора ведомого 1 Интерфейс UART_0, Сигнал готовности источника данных |

| 62 | PWR | AVCC | Питание аналоговых блоков 3,3 В | |

| 63 | PWR | AGND | Общий вывод аналоговых блоков | |

| 64 | I/O | PORT_1.13 | DAC_2 &I2C1_scl

GPIO_1.13 UART0_ndcd |

Канал ЦАП

Порт общего назначения Интерфейс I2C 1, сигнал тактирования Интерфейс UART_0, Сигнал обнаружения не-сущей |

Функции выводов ревизии 0

| Порт | Pad_control | ||||

|---|---|---|---|---|---|

| 00 | 01 | 02 | 03 | ||

| Порт 0 | 0.0 | SPI0_miso | GPIO_0.0 | Timer32_1_ch1 | REF_TST |

| 0.1 | SPI0_mosi | GPIO_0.1 | Timer32_1_ch2 | - | |

| 0.2 | SPI0_clk | GPIO_0.2 | Timer32_1_ch3 | ADC1.2 | |

| 0.3 | SPI0_n_ss_in | GPIO_0.3 | Timer32_1_ch4 | - | |

| 0.4 | SPI0_n_ss_out_0 | GPIO_0.4 | Timer32_1_Tx | ADC1.3 | |

| 0.5 | UART0_rxd | GPIO_0.5 | Timer16_0_in1 | - | |

| 0.6 | UART0_txd | GPIO_0.6 | Timer16_0_in2 | - | |

| 0.7 | UART0_cts | GPIO_0.7 | Timer16_0_out | ADC1.4 | |

| 0.8 | UART0_rts | GPIO_0.8 | Timer16_1_in1 | - | |

| 0.9 | I2C0_sda | GPIO_0.9 | Timer16_1_in2 | ADC1.5 | |

| 0.10 | I2C0_scl | GPIO_0.10 | Timer16_1_out | - | |

| 0.11 | TDI | GPIO_0.11 | Timer16_2_in1 | ADC1.6 | |

| 0.12 | TCK | GPIO_0.12 | Timer16_2_in2 | - | |

| 0.13 | TMS | GPIO_0.13 | Timer16_2_out | ADC1.7 | |

| 0.14 | TRSTn | GPIO_0.14 | - | - | |

| 0.15 | TDO | GPIO_0.15 | - | - | |

| Порт 1 | 1.0 | SPI1_miso | GPIO_1.0 | Timer32_2_ch1 | - |

| 1.1 | SPI1_mosi | GPIO_1.1 | Timer32_2_ch2 | - | |

| 1.2 | SPI1_clk | GPIO_1.2 | Timer32_2_ch3 | - | |

| 1.3 | SPI1_n_ss_in | GPIO_1.3 | Timer32_2_ch4 | - | |

| 1.4 | SPI1_n_ss_out_0 | GPIO_1.4 | Timer32_2_Tx | - | |

| 1.5 | SPI1_n_ss_out_1 | GPIO_1.5 | UART0_ck | ADC1.0 | |

| 1.6 | SPI1_n_ss_out_2 | GPIO_1.6 | UART0_ddis | - | |

| 1.7 | SPI1_n_ss_out_3 | GPIO_1.7 | digital_test_pad | ADC1.1 | |

| 1.8 | UART1_rxd | GPIO_1.8 | - | - | |

| 1.9 | UART1_txd | GPIO_1.9 | - | - | |

| 1.10 | UART1_cts | GPIO_1.10 | - | REF_ADC | |

| 1.11 | UART1_rts | GPIO_1.11 | - | REF_DAC | |

| 1.12 | I2C1_sda | GPIO_1.12 | UART0_ndtr | - | |

| 1.13 | DAC_2&I2C1_scl | GPIO_1.13 | - | ||

| 1.14 | SPI0_n_ss_out_1 | GPIO_1.14 | - | ||

| 1.15 | SPI0_n_ss_out_2 | GPIO_1.15 | TEST OUT | ||

| Порт 2 | 2.0 | SPIFI_SCLK | GPIO_2.0 | UART1_dtr | - |

| 2.1 | SPIFI_CS | GPIO_2.1 | UART1_dcd | - | |

| 2.2 | SPIFI_DATA_0 | GPIO_2.2 | UART1_dsr | - | |

| 2.3 | SPIFI_DATA_1 | GPIO_2.3 | UART1_ri | - | |

| 2.4 | SPIFI_DATA_2 | GPIO_2.4 | - | - | |

| 2.5 | SPIFI_DATA_3 | GPIO_2.5 | - | - | |

| 2.6 | SPI0_n_ss_out_3 | GPIO_2.6 | UART1_ck | - | |

| 2.7 | - | GPIO_2.7 | UART1_ddis | - | |

Функции выводов ревизии 2

| Порт | Pad_control | ||||

|---|---|---|---|---|---|

| 00 | 01 | 02 | 03 | ||

| Порт 0 | 0.0 | GPIO_0.0 | SPI0_miso | Timer32_1_ch1 | REF_TST |

| 0.1 | GPIO_0.1 | SPI0_mosi | Timer32_1_ch2 | - | |

| 0.2 | GPIO_0.2 | SPI0_clk | Timer32_1_ch3 | ADC1.2 | |

| 0.3 | GPIO_0.3 | SPI0_n_ss_in | Timer32_1_ch4 | - | |

| 0.4 | GPIO_0.4 | SPI0_n_ss_out_0 | Timer32_1_Tx | ADC1.3 | |

| 0.5 | GPIO_0.5 | UART0_rxd | Timer16_0_in1 | - | |

| 0.6 | GPIO_0.6 | UART0_txd | Timer16_0_in2 | - | |

| 0.7 | GPIO_0.7 | UART0_cts | Timer16_0_out | ADC1.4 | |

| 0.8 | GPIO_0.8 | UART0_rts | Timer16_1_in1 | - | |

| 0.9 | GPIO_0.9 | I2C0_sda | Timer16_1_in2 | ADC1.5 | |

| 0.10 | GPIO_0.10 | I2C0_scl | Timer16_1_out | - | |

| 0.11 | GPIO_0.11 | TDI | Timer16_2_in1 | ADC1.6 | |

| 0.12 | GPIO_0.12 | TCK | Timer16_2_in2 | - | |

| 0.13 | GPIO_0.13 | TMS | Timer16_2_out | ADC1.7 | |

| 0.14 | GPIO_0.14 | TRSTn | - | - | |

| 0.15 | GPIO_0.15 | TDO | - | - | |

| Порт 1 | 1.0 | GPIO_1.0 | SPI1_miso | Timer32_2_ch1 | - |

| 1.1 | GPIO_1.1 | SPI1_mosi | Timer32_2_ch2 | - | |

| 1.2 | GPIO_1.2 | SPI1_clk | Timer32_2_ch3 | - | |

| 1.3 | GPIO_1.3 | SPI1_n_ss_in | Timer32_2_ch4 | - | |

| 1.4 | GPIO_1.4 | SPI1_n_ss_out_0 | Timer32_2_Tx | - | |

| 1.5 | GPIO_1.5 | SPI1_n_ss_out_1 | UART0_ck | ADC1.0 | |

| 1.6 | GPIO_1.6 | SPI1_n_ss_out_2 | UART0_ddis | - | |

| 1.7 | GPIO_1.7 | SPI1_n_ss_out_3 | digital_test_pad | ADC1.1 | |

| 1.8 | GPIO_1.8 | UART1_rxd | - | - | |

| 1.9 | GPIO_1.9 | UART1_txd | - | - | |

| 1.10 | GPIO_1.10 | UART1_cts | - | REF_ADC | |

| 1.11 | GPIO_1.11 | UART1_rts | - | REF_DAC | |

| 1.12 | GPIO_1.12 | I2C1_sda | UART0_ndtr | - | |

| 1.13 | GPIO_1.13 | DAC_2&I2C1_scl | - | ||

| 1.14 | GPIO_1.14 | SPI0_n_ss_out_1 | - | ||

| 1.15 | GPIO_1.15 | SPI0_n_ss_out_2 | TEST OUT | ||

| Порт 2 | 2.0 | GPIO_2.0 | SPIFI_SCLK | UART1_dtr | - |

| 2.1 | GPIO_2.1 | SPIFI_CS | UART1_dcd | - | |

| 2.2 | GPIO_2.2 | SPIFI_DATA_0 | UART1_dsr | - | |

| 2.3 | GPIO_2.3 | SPIFI_DATA_1 | UART1_ri | - | |

| 2.4 | GPIO_2.4 | SPIFI_DATA_2 | - | - | |

| 2.5 | GPIO_2.5 | SPIFI_DATA_3 | - | - | |

| 2.6 | GPIO_2.6 | SPI0_n_ss_out_3 | UART1_ck | - | |

| 2.7 | GPIO_2.7 | - | UART1_ddis | - | |

Выводы, относящиеся к JTAG P0.11-P0.15 по-умолчанию сконфигурированы в режим 1. Остальные выводы - в режиме 0.

При запуске микроконтроллера в режиме SPIFI выводы P2.0-P2.5 при по-умолчанию автоматически инициализируются в режим 1, в иных вариантах загрузки выводы остаются в режиме 0.