Цифро-аналоговый преобразователь (ЦАП): различия между версиями

Нет описания правки |

|||

| (не показаны 3 промежуточные версии этого же участника) | |||

| Строка 1: | Строка 1: | ||

=== Введение. === | === Введение. === | ||

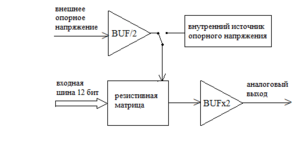

Модуль состоит из резистивного ЦАП, входного буфера/делителя внешнего опорного напряжения на 2, внутреннего ратиометрического источника опорного напряжения, выходного буфера с коэффициентом усиления два, а также дополнительных резисторов, ключей и цифровой управляющей логики. Схема с делением опорного напряжения пополам и последующего умножения напряжения на 2 выбрана для того, чтобы использовать только «тонкие» N-транзисторы в ключах, которые обеспечивают требуемое сопротивление в диапазоне напряжений от 0 до 0.6В при небольших размерах ключей, что позволяет минимизировать набросы при отсутствии буферизации между каскадами резистивной матрицы. Структурная схема представлена на рисунке | |||

[[Файл:DAC1.png|альт=Схема ЦАП|центр|мини|Схема ЦАП]] | |||

Резистивный ЦАП состоит из двух каскадов, каждый из которых обеспечивает разрешение шесть бит. Каждый единичный элемент каскада состоит одного резистора. Топологически эти элементы расположены симметрично относительно центра (common centroid) для уменьшения разброса параметров. Выходы первого каскада не буферизируются, поэтому для уменьшения систематической ошибки единичные элементы второго каскада имеют значительно большее сопротивление (1625 Ом по сравнению с 200 Ом). | |||

Выходной буфер представляет собой неинвертирующий операционный усилитель (ОУ) с коэффициентом усиления два. В остальных случаях – неинвертирующий ОУ с коэффициентом усиления один. Типичный ток потребления ОУ составляет 200мкА (не учитывая выходной ток). В выключенном состоянии типичный ток потребления ОУ составляет 30нА. | |||

=== Регистры управления === | |||

Для управления ЦАП используются регистры блока управления аналоговой подсистемой. Состав регистров управления ЦАП представлен в таблице ниже. | |||

==== Общий список регистров ==== | |||

=== | |||

{| class="wikitable" | {| class="wikitable" | ||

|+Регистры управления | |+Регистры управления ЦАП | ||

|Обозначение | |Обозначение | ||

|Смещение | |Смещение | ||

| Строка 39: | Строка 18: | ||

|Доступ | |Доступ | ||

|- | |- | ||

| | |DAC1_CFG | ||

| | |0x00 | ||

|0x0 | |0x0 | ||

|Регистр | |Регистр настойки ЦАП1 | ||

|RW | |RW | ||

|- | |- | ||

| | |DAC2_CFG | ||

| | |0x04 | ||

|0x0 | |0x0 | ||

| | |Регистр настойки ЦАП2 | ||

|RW | |RW | ||

|- | |- | ||

| | |DAC1_VALUE | ||

| | |0x08 | ||

|0x0 | |0x0 | ||

| | |Входные данные для ЦАП1 | ||

|WO | |WO | ||

|- | |- | ||

| | |DAC2_VALUE | ||

| | |0x0С | ||

|0x0 | |0x0 | ||

| | |Входные данные для ЦАП2 | ||

| | |WO | ||

|} | |||

==== Описание регистров ==== | |||

===== DACx_CFG ===== | |||

Смещение: 0x00+x*4 - конфигурационный регистр. Значение после подачи сброса: 0x00000000; | |||

{| class="wikitable" | |||

|31 | |||

|30 | |||

|29 | |||

|28 | |||

|27 | |||

|26 | |||

|25 | |||

|24 | |||

|23 | |||

|22 | |||

|21 | |||

|20 | |||

|19 | |||

|18 | |||

|17 | |||

|16 | |||

|- | |- | ||

| | | colspan="15" |Зарезервировано | ||

| | |||

| | |||

| | |||

|- | |- | ||

| | |rw | ||

| | |rw | ||

| | |rw | ||

| | |rw | ||

| | |rw | ||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|} | |} | ||

{| class="wikitable" | |||

|15 | |||

|14 | |||

|13 | |||

|12 | |||

|11 | |||

|10 | |||

|9 | |||

|8 | |||

|7 | |||

|6 | |||

|5 | |||

|4 | |||

|3 | |||

|2 | |||

|1 | |||

|0 | |||

|- | |||

| colspan="4" |Зарезервировано | |||

|Ext_Clb | |||

|ExtRef | |||

| colspan="8" |Div | |||

|Rn | |||

|EN | |||

|- | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|ro | |||

|}Бит 11 '''Ext_Clb''' - Выбор источника внешнего опорного напряжения: | |||

* 1 - внешний вывод; | |||

* 0 - настраиваемый ОИН | |||

Бит 10 '''ExtRef''' - Выбор источника опорного напряжения: | |||

* 1 - внешний; | |||

* 0 - встроенный | |||

Биты 9:2 '''Div''' - Значение делителя тактового сигнала. Частота определяется как F<sub>ЦАП</sub>=F<sub>IN</sub>/(Div+1) | |||

Бит 1 '''Rn''' - Управление сбросом ЦАП, активный уровень «0»: | |||

* 1 - сброс деактивирован; | |||

* 0 - сброс активирован | |||

Бит 0 '''EN''' - Управление питанием ЦАП: | |||

* 0 – выключен; | |||

* 1 – включен | |||

===== | ===== DACx_VALUE ===== | ||

Смещение: 0x08+x*4 - регистр данных. Значение после подачи сброса: 0x00000000; | |||

{| class="wikitable" | |||

|31 | |||

|30 | |||

|29 | |||

|28 | |||

|27 | |||

|26 | |||

|25 | |||

|24 | |||

|23 | |||

|22 | |||

|21 | |||

|20 | |||

|19 | |||

|18 | |||

|17 | |||

|16 | |||

|- | |||

| colspan="15" |Зарезервировано | |||

| | |||

|- | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|} | |||

{| class="wikitable" | |||

|15 | |||

|14 | |||

|13 | |||

|12 | |||

|11 | |||

|10 | |||

|9 | |||

|8 | |||

|7 | |||

|6 | |||

|5 | |||

|4 | |||

|3 | |||

|2 | |||

|1 | |||

|0 | |||

|- | |||

| colspan="4" |Зарезервировано | |||

| colspan="12" |Data | |||

|- | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|ro | |||

|}Бит 11:0 '''Data''' - Входные данные для преобразования в аналоговый сигнал | |||

Текущая версия от 15:46, 12 мая 2023

Введение.

Модуль состоит из резистивного ЦАП, входного буфера/делителя внешнего опорного напряжения на 2, внутреннего ратиометрического источника опорного напряжения, выходного буфера с коэффициентом усиления два, а также дополнительных резисторов, ключей и цифровой управляющей логики. Схема с делением опорного напряжения пополам и последующего умножения напряжения на 2 выбрана для того, чтобы использовать только «тонкие» N-транзисторы в ключах, которые обеспечивают требуемое сопротивление в диапазоне напряжений от 0 до 0.6В при небольших размерах ключей, что позволяет минимизировать набросы при отсутствии буферизации между каскадами резистивной матрицы. Структурная схема представлена на рисунке

Резистивный ЦАП состоит из двух каскадов, каждый из которых обеспечивает разрешение шесть бит. Каждый единичный элемент каскада состоит одного резистора. Топологически эти элементы расположены симметрично относительно центра (common centroid) для уменьшения разброса параметров. Выходы первого каскада не буферизируются, поэтому для уменьшения систематической ошибки единичные элементы второго каскада имеют значительно большее сопротивление (1625 Ом по сравнению с 200 Ом).

Выходной буфер представляет собой неинвертирующий операционный усилитель (ОУ) с коэффициентом усиления два. В остальных случаях – неинвертирующий ОУ с коэффициентом усиления один. Типичный ток потребления ОУ составляет 200мкА (не учитывая выходной ток). В выключенном состоянии типичный ток потребления ОУ составляет 30нА.

Регистры управления

Для управления ЦАП используются регистры блока управления аналоговой подсистемой. Состав регистров управления ЦАП представлен в таблице ниже.

Общий список регистров

| Обозначение | Смещение | Начальное значение | Назначение | Доступ |

| DAC1_CFG | 0x00 | 0x0 | Регистр настойки ЦАП1 | RW |

| DAC2_CFG | 0x04 | 0x0 | Регистр настойки ЦАП2 | RW |

| DAC1_VALUE | 0x08 | 0x0 | Входные данные для ЦАП1 | WO |

| DAC2_VALUE | 0x0С | 0x0 | Входные данные для ЦАП2 | WO |

Описание регистров

DACx_CFG

Смещение: 0x00+x*4 - конфигурационный регистр. Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Зарезервировано | Ext_Clb | ExtRef | Div | Rn | EN | ||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ro |

Бит 11 Ext_Clb - Выбор источника внешнего опорного напряжения:

- 1 - внешний вывод;

- 0 - настраиваемый ОИН

Бит 10 ExtRef - Выбор источника опорного напряжения:

- 1 - внешний;

- 0 - встроенный

Биты 9:2 Div - Значение делителя тактового сигнала. Частота определяется как FЦАП=FIN/(Div+1)

Бит 1 Rn - Управление сбросом ЦАП, активный уровень «0»:

- 1 - сброс деактивирован;

- 0 - сброс активирован

Бит 0 EN - Управление питанием ЦАП:

- 0 – выключен;

- 1 – включен

DACx_VALUE

Смещение: 0x08+x*4 - регистр данных. Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Зарезервировано | Data | ||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | ro |

Бит 11:0 Data - Входные данные для преобразования в аналоговый сигнал