Блок прямого доступа к памяти (ПДП)

Введение

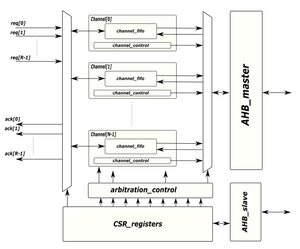

Специализированный контроллер прямого доступа к памяти (ПДП) реализует передачу данных между ведомыми устройствами на коммутационной матрице без участия микроконтроллера, поддерживая аппаратное адресное обращение к доменам MCU32, участвующими в обмене данными.

Контроллер ПДП имеет 4 независимых каналов, обеспечивающих работу в режимах память-память, периферия-периферия, память-периферия.

Каждый из каналов ПДП имеет программируемый уровень приоритетов обработки запросов, задаваемый пользователем.

При работе с периферией контроллер ПДП, контролирует состояние внутренних буферов периферийных устройств с автоматической обработкой забросов и сигналов подтверждения. Структурная схема ПДП контроллера изображена на рисунке

Доступ к шине

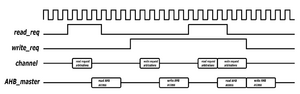

Контроллер управления шиной (AHB_master), при наличии данных в каналах ПДП, реализует непрерывный доступ к шине. При поддержке программных настроек управления сигнала подтверждения (нужен не для всех периферийный блоков) время выставлений транзакций на шину различается.

Сеанс передачи данных, начинается с чтения требуемых данных источника, заполнения буфера канала до указанного уровня, записи данных по адресу назначения, и далее в цикле пока не будет осуществлена требуемая передача данных.

Инициация трансфера данных происходит по сигналам запросов для каждого из канала, включая запросы на чтение и запись. При транзакциях памяти, внутренний сигнал запроса всегда активен.

Сигнал запроса на запись обрабатывается только тогда, когда в буфере канала есть данные. В случае конфликтов при формировании внутренних сигналов запросов со стороны конечных автоматов каналов, запросы обрабатываются в соответствии с установленным уровнем приоритета каждого из каналов. В случае совпадения уровней программного приоритета, обрабатывается запрос в соответствии с уровнем статического приоритета, равному номеру канала (младший канал имеет наивысший приоритет).

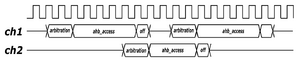

Примеры доступа к шине показаны на временных диаграммах, на рисунках ниже (длительность доступа к шине показана условно в 3 такта).

Арбитраж

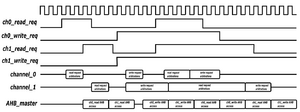

Арбитраж выбора канала происходит за два такта удержания линии запроса. Если одновременно поступают несколько запросов ПДП, то схема арбитража выбирает наиболее приоритетную линию запроса в соответствии с программной установкой каждого из каналов, которые поддерживают четыре уровня приоритетов:

- приоритетный (очень высокой);

- высокий;

- средний;

- низкий.

В случае активности одного канала, запрос не может быть обработан немедленно: после завершения обработки запроса добавляется один такт на выключение канала (или обработки сигнала подтверждения) и два такта для обработки нового запроса.

При работе нескольких каналов возможна параллельная обработка запросов, при этом, запросы с текущего рабочего канала при осуществлении арбитража маскируются для корректного выключения канала (или передачи сигнала подтверждения). Временные диаграммы работы изображены на рисунке

Тактирование каналов

Для каждого из каналов предусмотрено автоматическое перекрытие тактирования на основе сигнала разрешения работы канала.

После завершения выполнения задания или обнаружения ошибки происходит автоматический сброс канала, и переход конечного автомата контроллера канала в состояние IDLE.

При этом каждый из каналов сохраняет состояния регистров, на котором была завершена его работа.

Выключение каналов

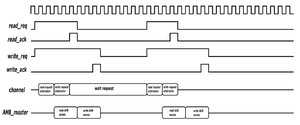

При передаче команды выключения каналу происходит перекрытие тактирования канала, после которого канал полностью сбрасывается.

В случае передачи команды выключения во время транзакции, мастер-интерфейс контроллера завершает начатую передачу блока данных в соответствии с установкой канала, при этом данные передаваемые после выключения не являются валидными. Временная диаграмма представлена на рисунке

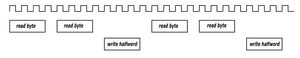

Блочные транзакции

Контроллер ПДП предусматривает возможность трансфера блочных транзакций, поддерживая смешанную передачу данных. К примеру, чтение байтового буфера и запись слов. При этом, вводимые значения для трансфера данных должны находится в строгом соотношении с вводимым значением длины пересылки и делением на блоки при чтении и записи. Примеры организации блочных транзакций показаны на временных диаграммах ниже (рисунки 8–10):

- чтение байтов, запись полуслова. Длина пересылки: 4 байта, размер блока чтения: 1 байт, размер блока записи 2 байта;

- чтение байтов, запись полуслова. Длина пересылки: 4 байта, размер блока чтения: 1 байт, размер блока записи 4 байта;

- чтение байтов, запись полуслова. Длина пересылки: 4 байта, размер блока чтения: 2 байт, размер блока записи 4 байта.

В случае ввода значений, не удовлетворяющих делению на блоки или ввода значений превышающих размер буфера канала возможно непредвиденное поведение контроллера.

Формирование прерываний

Контроллер ПДП поддерживает три типа маскируемых прерываний:

- прерывания каналов о завершении задания;

- глобальное прерывание о завершении всех заданий;

- прерывание об ошибке.

Прерывания каналов формируются в случае установки разрешения на прерывания, по умолчанию выключены.

Глобальное прерывание формируется при выполнении контроллером всех поставленных задач, по умолчанию включено.

Контроллер ПДП формирует ошибку на основе отклика об ошибке со стороны шины. Канал, обнаруживший ошибку, завершает свою задачу. Остальные каналы могут продолжать свою работу.

Передача в режиме периферии.

В режиме передачи с периферийными устройствами от устройства формируется запрос на транзакцию чтения или записи. Контроллер позволяет соотнести любой канал с периферийным устройством. Для настройки соответствия канала и линии от периферийного устройства используются поля Read requets, Write requets регистра Config. Соответствие между значениями этих полей и линиями периферии представлено в таблице

| Устройство | Значение Read requets/ Write requets |

| USART_0 | 0 |

| USART_0 | 1 |

| CRYPTO | 2 |

| SPI_0 | 3 |

| SPI_1 | 4 |

| I2C_0 | 5 |

| I2C_1 | 6 |

| SPIFI | 7 |

| Timer32_1 | 8 |

| Timer32_2 | 9 |

| DAC0 | 10 |

| DAC1 | 11 |

| Timer32_0 | 12 |

Чтение статуса каналов

Для каждого из каналов, поддерживается возможность чтения текущих значений счёта (текущий адрес чтения/записи, количество переданных слов) и значений которые были установлены при настройке канала (инициализирующий адрес чтения/записи, количество слов для передачи).

Статус каналов доступен по адресам конфигурационных регистров каналов при доступе на чтение. При этом каждый из адресов возвращает значение в соответствии с установленным значением Current_Value регистра DMA_CNTR.

В случае установки бита Current_Value будут возвращаться значения текущего счёта, в противном случае будут возвращаться значения, установленные при настройке канала. В данном случае будут возвращены данные в соответствии с таблицей:\

| Регистр | Поля регистра | Описание |

| Destination | 31:0 | Возвращает последнюю переданную подзадачу контроллера канала.

В случае ошибки записи содержит указатель на текущий адрес мастер-интерфейса |

| Source | 31:0 | Возвращает текущую подзадачу контроллера канала.

Current_ch_read_task - 2Read block size

|

| Len | 31:0 | Возвращает счётчик байт подзадач контроллера.

счётчик байт подзадач обновляется только по подзадачам записи.

If (state==write): Current byte len - 2Write block size If (state==read): Current byte len |

| Config | 0 | Регистр состояния ошибки при записи

0 – ошибки не было; 1 – была зафиксирована ошибка шины при чтении |

| Config | 1 | Регистр состояния ошибки при чтении

0 – ошибки не было; 1 – была зафиксирована ошибка шины при записи |

| Config | 3:2 | Регистр состояния статуса контроллера канала

01 – канал в состоянии чтения; 10 – канала в состоянии записи |

Регистры контроллера ПДП

Регистры контроллера включают регистры настройки параметров и управление каждым каналом и глобальный регистр статуса и прерываний. Регистры контроллера представлены в следующей таблице. Доступ к регистрам осуществляется только словами по 32 бита.

Список регистров

| Адрес/смещение | Описание регистра | Название | Доступ |

| 0x00 | Регистр адреса назначения канала 1 | CH1_DST | R/W |

| 0x04 | Регистр адреса источника канала 1 | CH1_SRC | R/W |

| 0x08 | Регистр размера передаваемых данных канала 1 | CH1_LEN | R/W |

| 0x0C | Регистр управления и конфигурации канала 1 | CH1_CFG | R/W |

| 0x10 | Регистр адреса назначения канала 2 | CH2_DST | R/W |

| 0x14 | Регистр адреса источника канала 2 | CH2_SRC | R/W |

| 0x18 | Регистр размера передаваемых данных канала 2 | CH2_LEN | R/W |

| 0x1C | Регистр управления и конфигурации канала 2 | CH2_CFG | R/W |

| 0x20 | Регистр адреса назначения канала 3 | CH3_DST | R/W |

| 0x24 | Регистр адреса источника канала 3 | CH3_SRC | R/W |

| 0x28 | Регистр размера передаваемых данных канала 3 | CH3_LEN | R/W |

| 0x2C | Регистр управления и конфигурации канала 3 | CH3_CFG | R/W |

| 0x30 | Регистр адреса назначения канала 4 | CH4_DST | R/W |

| 0x34 | Регистр адреса источника канала 4 | CH4_SRC | R/W |

| 0x38 | Регистр размера передаваемых данных канала 4 | CH4_LEN | R/W |

| 0x3C | Регистр управления и конфигурации канала 4 | CH4_CFG | R/W |

| 0x40 | Регистр прерываний и настройки контроллера | DMA_CNTR | R/W |

Описание регистров

Регистры CHx_DST

Смещение: 0x00+(x-1)*0x10, x - номер канала (от 1 до 4). Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| DST_ADDR 31:16 | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| DST_ADDR 16:0 | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 31:0 DST_ADDR - 32-х битный регистр "адреса назначения" данных канала.

Регистры CHx_SRC

Смещение: 0x04+(x-1)*0x10, x - номер канала (от 1 до 4). Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| SRC_ADDR 31:16 | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SRC_ADDR 16:0 | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 31:0 SRC_ADDR - 32-х битный регистр "адреса источника" данных канала.

Регистры CHx_LEN

Смещение: 0x08+(x-1)*0x10, x - номер канала (от 1 до 4). Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| LEN 31:16 | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LEN 15:0 | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 31:0 LEN - 32-х битный регистр LEN формирует количество байт для пересылки. Количество пересылаемых данных , определяется как LEN+1.

Регистры CHx_CFG

Смещение: 0x0C+(x-1)*0x10, x - номер канала (от 1 до 4). Значение после подачи сброса: 0x00000000;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| r31 | r30 | r29 | r28 | Irq_ena | Write_ack

_ena |

Read_

ack_ena |

Write_requets | Read_requets | Write

_block_size | ||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Write_

block_size |

Read_

block_size |

Write

_size |

Read

_size |

Write

_incr |

Read

_incr |

Write

_mode |

Read

_mode |

Prior | EN | ||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Бит 27 Irq_ena - Разрешение формирования прерывания по завершении работы канала:

- 0 – прерывание не формируется;

- 1 – прерывание формируется

Бит 26 Write_ack_ena - Разрешение работы логики с откликом для адресата назначения:

- 0 – запрещено;

- 1 – разрешено

Бит 25 Read_ack_ena - Разрешение работы логики с откликом для адресата источника:

- 0 – запрещено;

- 1 – разрешено

Бит 24:21 Write_requets - Выбор периферийной линии назначения.

Бит 20:17 Read_requets - Выбор периферийной линии источника.

Бит 16:14 Write_block_size - Количество байт в пакете*:

- Определяется как 2 write_block_size* должно быть кратно read_size

Бит 13:11 Read_block_size - Количество байт в пакете*:

- Определяется как 2 write_block_size* должно быть кратно read_size

Бит 10:9 Write_size - Разрядность адреса назначения*:

- 00 – байт;

- 01 – полуслово;

- 10 – слово;

- 11 - резерв* должно быть кратно data_len

Бит 8:7 Read_size - Разрядность адреса источника*:

- 00 – байт;

- 01 – полуслово;

- 10 – слово;

- 11 - резерв* должно быть кратно data_len

Бит 6 Write_incr - Инкремент адреса назначения:

- 0 – нет инкремента;

- 1 – есть инкремент

Бит 5 Read_incr - Инкремент адреса источника:

- 0 – нет инкремента;

- 1 – есть инкремент

Бит 4 Write_mode - Режим адреса назначения:

- 0 – периферия;

- 1 – память

Бит 3 Read_mode - Режим адреса источника:

- 0 – периферия;

- 1 – память

Бит 2:1 Prior - Приоритет канала:

- 00 – низкий;

- 01 – средний;

- 10- высокий;

- 11 – приоритетный (очень высокий)

Бит 0 EN - Разрешение работы канала:

- 1 – инициализация работы канала;

- 0 – принудительная остановка

Регистр DMA_CNTR

Смещение: 0x40, Значение после подачи сброса: 0x????????; Регистр обеспечивает управление прерываниями каналов и контроллера в целом. Функции отдельных полей регистра отличаются при выполнении операции чтения и записи. Старшие два байта всегда зарезервированы.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Зарезервировано | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

На запись

Далее следует описание значения полей на "запись". Доступ на установку регистров разрешения прерываний возможен только при отсутствии установки на снятие запроса линии прерывания.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Current

_Value |

Error_

Irq_Ena |

Global_

Irq_Ena |

Clear_

Error_Irq |

Clear_

Global_Irq |

IC4 | IC3 | IC2 | IC1 | |||||||

| w | w | w | w | w | w | w | w | w | w | w | w | w | w | w | w |

Бит 8 Current_Value - Разрешение чтения текущего статуса канала:

- 1 – разрешено;

- 0 – запрещено

Бит 7 Error_Irq_Ena - Разрешение формирования прерывания при ошибке:

- 1 - разрешено;

- 0 -запрещено

Бит 6 Global_Irq_Ena - Разрешение формирования глобального прерывания:

- 1 – разрешено;

- 0 – запрещено

Бит 5 Clear_Error_Irq - Очистка прерывания ошибки:

- Запись 1 – вызывает снятие запроса на прерывание

Бит 4 Clear_Global_Irq - Очистка глобального прерывания:

- Запись 1 – вызывает снятие запроса на прерывание

Бит 3 IC4 - Очистка локального прерывания от 4 канала:

- Запись 1 – вызывает снятие запроса на прерывание

Бит 2 IC3 - Очистка локального прерывания от 3 канала:

- Запись 1 – вызывает снятие запроса на прерывание

Бит 1 IC2 - Очистка локального прерывания от 2 канала:

- Запись 1 – вызывает снятие запроса на прерывание

Бит 0 IC1 - Очистка локального прерывания от 1 канала:

- Запись 1 – вызывает снятие запроса на прерывание

На чтение

Далее следует описание значения полей на "чтение". Примечание – При передаче каналу нового задания, значения Channel_Bus_Error сбрасываются в 0.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CCV | E4 | E3 | E2 | E1 | I4 | I3 | I2 | I1 | R4 | R3 | R2 | R1 | |||

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Бит 12 CCV - Channel_Current_Value. Статус чтения состояния каналов:

- 0 - текущие значения;

- 1 - значения при настройке

Бит 11 E4. Статус состояния канала 4 при ошибках на шине:

- 0 - нет ошибки;

- 1 - есть ошибка

Бит 10 E3. Статус состояния канала 3 при ошибках на шине:

- 0 - нет ошибки;

- 1 - есть ошибка

Бит 9 E2. Статус состояния канала 2 при ошибках на шине:

- 0 - нет ошибки;

- 1 - есть ошибка

Бит 8 E1. Статус состояния канала 1 при ошибках на шине:

- 0 - нет ошибки;

- 1 - есть ошибка

Бит 7 I4. Статус прерывания канала 4:

- 1 - есть прерывания;

- 0 - нет прерываний

Бит 6 I3. Статус прерывания канала 3:

- 1 - есть прерывания;

- 0 - нет прерываний

Бит 5 I2. Статус прерывания канала 2:

- 1 - есть прерывания;

- 0 - нет прерываний

Бит 4 I1. Статус прерывания канала 1:

- 1 - есть прерывания;

- 0 - нет прерываний

Бит 3 R4. Статус состояния канала 4:

- 1 - готов к работе;

- 0 - занят

Бит 2 R3. Статус состояния канала 3:

- 1 - готов к работе;

- 0 - занят

Бит 1 R2. Статус состояния канала 2:

- 1 - готов к работе;

- 0 - занят

Бит 0 R1. Статус состояния канала 1:

- 1 - готов к работе;

- 0 - занят