Ускоритель CRC: различия между версиями

| Строка 22: | Строка 22: | ||

==== Описание регистров ==== | ==== Описание регистров ==== | ||

=====Регистр DATA===== | |||

Смещение: 0x0, Значение после подачи сброса: 0x????????; | |||

{| class="wikitable" | |||

|31 | |||

|30 | |||

|29 | |||

|28 | |||

|27 | |||

|26 | |||

|25 | |||

|24 | |||

|23 | |||

|22 | |||

|21 | |||

|20 | |||

|19 | |||

|18 | |||

|17 | |||

|16 | |||

|- | |||

|D31 | |||

|D30 | |||

|D29 | |||

|D28 | |||

|D27 | |||

|D26 | |||

|D25 | |||

|D24 | |||

|D23 | |||

|D22 | |||

|D21 | |||

|D20 | |||

|D19 | |||

|D18 | |||

|D17 | |||

|D16 | |||

|- | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|} | |||

{| class="wikitable" | |||

|15 | |||

|14 | |||

|13 | |||

|12 | |||

|11 | |||

|10 | |||

|9 | |||

|8 | |||

|7 | |||

|6 | |||

|5 | |||

|4 | |||

|3 | |||

|2 | |||

|1 | |||

|0 | |||

|- | |||

|D15 | |||

|D14 | |||

|D13 | |||

|D12 | |||

|D11 | |||

|D10 | |||

|D9 | |||

|D8 | |||

|D7 | |||

|D6 | |||

|D5 | |||

|D4 | |||

|D3 | |||

|D2 | |||

|D1 | |||

|D0 | |||

|- | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|rw | |||

|}Биты 31:0 D'''y''' - Биты линий прерываний, отвечающие за деактивацию срабатывания прерывания по фронту (y=0...31) | |||

При записи: | |||

*0: соответствующая линия прерывания не меняет тип | |||

*1: соответствующая линия прерывания деактивируется на срабатывание по фронту | |||

При чтении текущее состояние линии прерывания | |||

*0: прерывание не срабатывает по фронту | |||

*1: прерывание срабатывает по фронту | |||

Версия от 18:10, 17 апреля 2023

Общее описание

Блок предназначен для вычисления циклической контрольной суммы (CRC) массива данных без использования вычислительных ресурсов центрального процессора.

Инструкции работы с блоком

Введение

Блок вычисления контрольных сумм находится на шине AHP и доступен по очереди с APB_P и Ускорителем криптографии.

Описание работы с модулем CRC

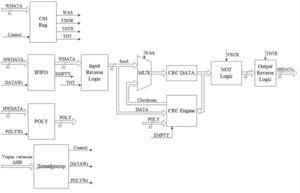

Контроллер состоит из следующих компонентов:

- дешифратора системных сигналов шины AHB,

- регистра управления CtrlReg,

- регистра полинома POLY Reg,

- входного буфера IFIFO объемом 16 слов по 32 бита,

- логики перестановки битов входных данных Input Reverse Logic,

- устройства кодирования CRC_Engine с мультиплексором MUX и сдвиговым регистром CRC DATA,

- логики инверсии NOT Logic и логики перестановки битов выходных данных Output Reverse Logic.

Дешифратор системных сигналов формирует сигналы чтения и записи всех регистров контроллера в соответствии с адресным пространством. Регистр управления CtrlReg управляет всеми настройками процесса вычисления суммы. Регистр полинома POLY Reg предназначен для хранения значения полинома. Входной буфер IFIFO осуществляет буферизацию входных данных, по которым будет считаться контрольная сумма. Этот буфер, а также регистры управления и полинома подключены напрямую к шине HWDATA. При полном заполнении буфера активизируется сигнал HREADY_o, останавливающий транзакцию по шине AHB. Логика перестановки битов входных данных предназначена для перестановки битов и байтов слова входных данных и управляется битами поля TOT регистра управления. Устройство кодирования CRC_Engine с мультиплексором MUX и сдвиговым регистром CRC DATA производят вычисление контрольной суммы последовательности входных данных. Вычисленная контрольная сумма записывается в выходной регистр логики перестановки битов выходных данных Output Reverse Logic через логику инверсии NOT Logic, которая инвертирует или не инвертирует выходные данные в зависимости от значения бита FXOR регистра управления. Логика перестановки битов выходных данных предназначена для перестановки битов и байтов слова вычисленной контрольной суммы и управляется битами поля TOTR регистра управления. Выходные биты контрольной суммы подключены напрямую к шине HRDATA.

Карта регистров блока приведена в таблице ниже. Запись данных в регистр данных может осуществляться в 8, 16 или 32-разрядном режиме. Доступ к остальным регистрам осуществляется только в 32-разрядном режиме.

Описание регистров

Регистр DATA

Смещение: 0x0, Значение после подачи сброса: 0x????????;

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| D31 | D30 | D29 | D28 | D27 | D26 | D25 | D24 | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Биты 31:0 Dy - Биты линий прерываний, отвечающие за деактивацию срабатывания прерывания по фронту (y=0...31)

При записи:

- 0: соответствующая линия прерывания не меняет тип

- 1: соответствующая линия прерывания деактивируется на срабатывание по фронту

При чтении текущее состояние линии прерывания

- 0: прерывание не срабатывает по фронту

- 1: прерывание срабатывает по фронту